Other Parts Discussed in Thread: LMK04828, ADS54J60EVM, ADS54J60

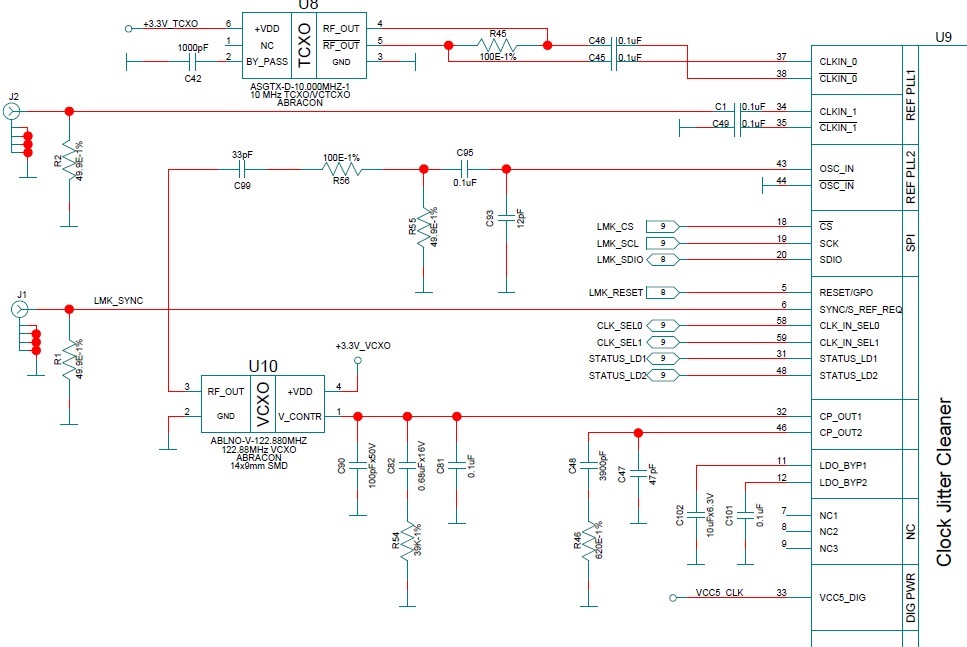

We are having issues trying to get PLL1 to lock. Attached is the TCS file used. Regardless of using either an on board 10MHz source or external source PLL1 never locks. The design is based upon the LMK04828EVM board.

An interesting note... when the device is placed in clock distribution mode and a 100MHz clock is applied to CLKIN1. A clock output with no division is much less stable than the input. The input is 0.5PPM stable however the output is 500PPM. Also if the "divider only" option is selected the output drops to ~3.2MHz and doesn't really resemble a clock.

Any help would be appreciated.

Regards, GaryLMK04828 VCO0_2400MHz.tcs