Other Parts Discussed in Thread: LMK04806, LMK04832

Hi Sir,

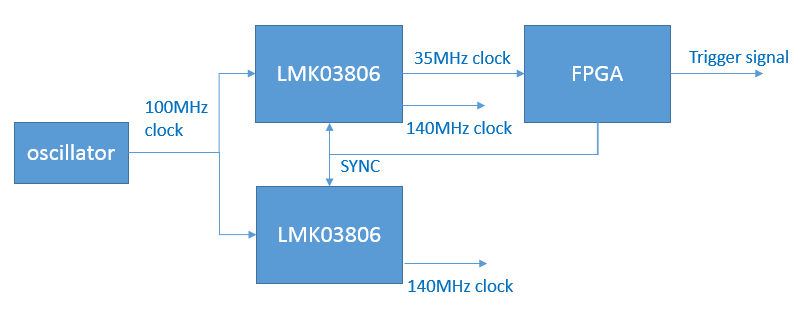

Below is a diagram of my design, as you can see I use the same FPGA pin to assert the "SYNC" signal of two LMK03806, so I am expecting the two 140MHz clock output are synchronized both in frequency and phase.

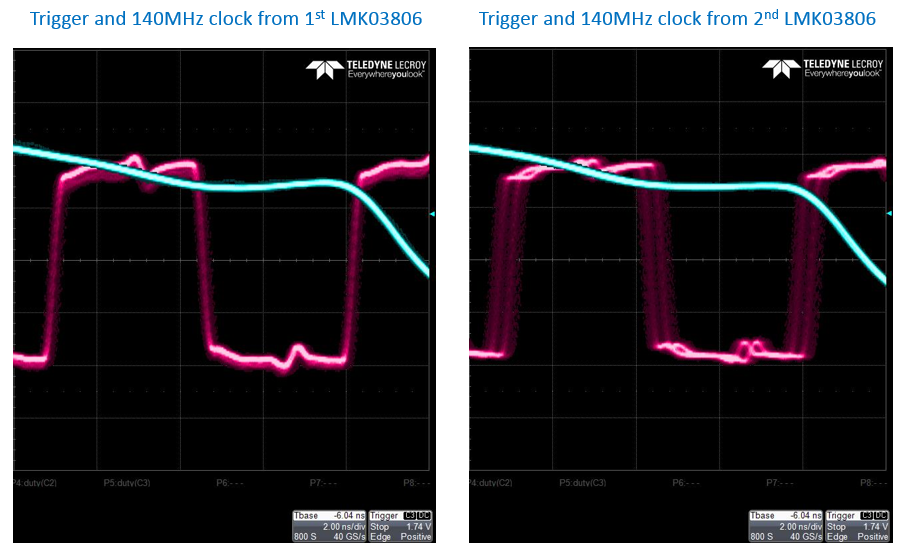

However, when I use the "Trigger signal" from FPGA as the triggering channel of oscilloscope, and measure the 140MHz clock from two LMK03806 separately, I found the 140MHz clock of the 1st LMK03806 synchronizes with trigger signal perfectly, however, obviously a ~0.4ns jitter can be observed on the 140MHz clock of the 2nd LMK03806.

Since the VCO inside LMK03806 is set to 2500MHz, 0.4ns is close to one clock period so I suspect there is something wrong on the SYNC mechanism, appreciated if there is any way to solve this problem, thanks !