Hi, all!

In I2C mode, what should I do with unused pins which are SEC_REFx pins and VDD_SEC_REF pin of CDCM6208?.

It may be a special case peculiar to a customer,,,,,,,

1. SEC_REFx pins are left open, and VDD_SEC_REF pin is connected to 3V_VDD.

- In this case, CDCM6208 sometimes cannot connect with HOST.

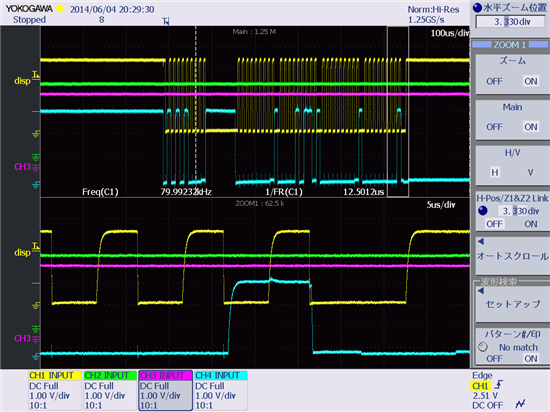

It seems that the I2C timing and ramp-up/down are satisfied with the I2C specification.

- When only CDCM6208 is mounted without FPGAs and other ICs on the same PCB,

CDCM6208 can connect with HOST completely.

2. When VDD_SEC_REF is left open or is connected to GND, CDCM6208 can communicate with HOST completely.

Regards,

Toshi