Hi,

I will use LMK04828 as a clock/sysref distribution/generation circuit only, no internal PLL nor VCO are used.

Input clock on CLKin1 and all DCLK and SDCLK outputs are used as LVDS.

Actual state of schematic is base on ADC12J4000EVM and DAC3XJ8XEVM schematics.

My questions are about power supply filtering and bypass capacitors:

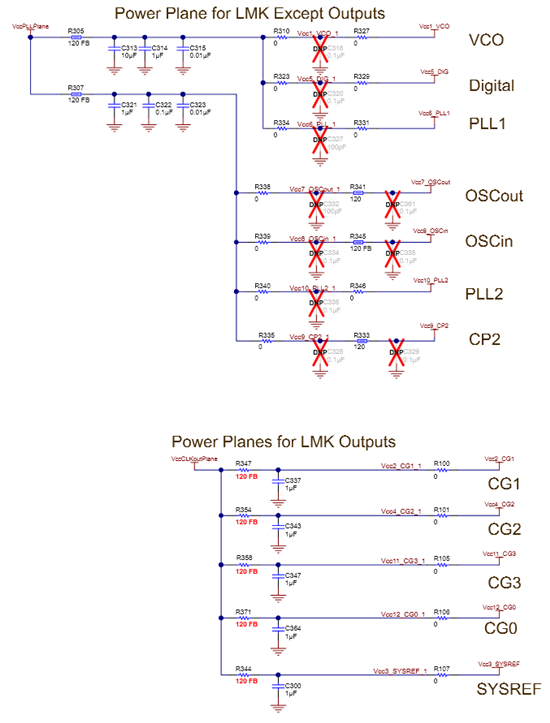

DAC3XJ8XEVM gives the following power tree:

- +3.3VCLK: 33uF, 10uF, 100nF, 7x10nF

- Bead => VCC1, VCC2 : 1uF, 100nF, 10nF

- Bead => VCC8, VCC10 : 1uF, 100nF, 10nF

- Bead => VCC7

- Bead => VCC9

- Bead => VCC2

- Bead => VCC3

- Bead => VCC4

- Bead => VCC11

- Bead => VCC12

ADC12J4000EVM gives the following power tree:

- VIO_3P3V_LMK_PLL: 10uF, 1uF, 9x100nF

- VCC1, VCC5, VCC7, VCC8, VCC10

- Bead => VCC2: 100nF

- Bead => VCC3: 100nF

- Bead => VCC4: 100nF

- Bead => VCC6: 100nF

- Bead => VCC9: 100nF

- Bead => VCC11: 100nF

- Bead => VCC12: 100nF

In clock distribution mode what would be the effect of using a single 3.3V for all VCC?

Can we estimate the power consumption of 3.3V power rail in clock distribution mode?

Thanks and regards