Dear All,

I am using CDCE62005 to generate some frequency in my design.

Reference clock = 76.8MHz,

OUT0、OUT1 、OUT2 = 122.88MHz,

OUT3 、OUT4 = 38.4MHz,

AUX_OUT = 61.44MHz.

But I find some problem in my tests.

Case 1:

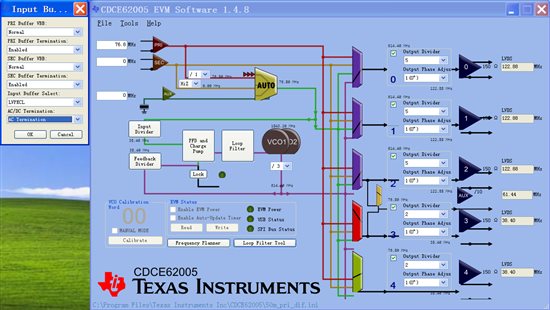

I use 76.8MHz differential reference clock into primary reference clock (PRI_REF) .The GUI setup see underside picture.

The GUI result is:

REGISTERS

0 EB860320

1 EB860301

2 EB860302

3 EB800003

4 EB800114

5 18040BE5

6 149E0126

7 BD91FDE7

8 80001808

PORTS

0 DD

1 FF

2 DF

3 F9

INPUTS

PRI 76.8

SEC 0

AUX 0

EXTERNAL COMPONENTS

C4 1

R4 1

C5 1

I’m writing this configure value into the registers of CDCE62005 using SPI.

OUT3 and OUT4 is right, so the input clock is alrigh and recognized.

The problem is that PLL is not locked with this configure value.

Why the PLL is not locked? what is the problem?

Case 2:

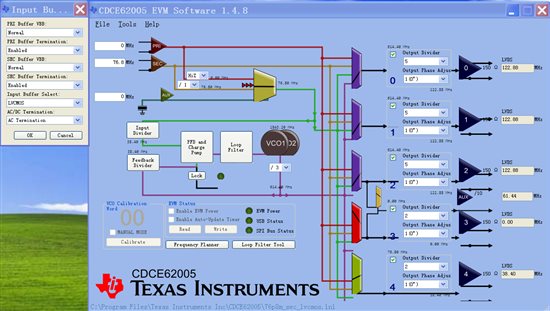

I use 76.8MHz LVCMOS reference clock into secondary reference clock (SEC_REF) .The GUI setup see underside picture.

The GUI result is:

REGISTERS

0 EB860300

1 EB860321

2 EB860302

3 EB800003

4 EB800114

5 18040A85

6 149E0126

7 BD91FDE7

8 80001808

PORTS

0 DD

1 FF

2 DF

3 F9

INPUTS

PRI 0

SEC 76.8

AUX 0

EXTERNAL COMPONENTS

C4 1

R4 1

C5 1

I’m writing this configure value into the registers of CDCE62005 using SPI.

The problem is PLL is locked with these value.But the output of OUT0、OUT1 and OUT2 is 130MHz —— the expected frequency is 122.88MHz.

It seems the VCO is not working correctly. What is the problem?

How am I supposed to solve these two problems of case 1 and case 2? Can you help me?

thank you!!