Dear all,

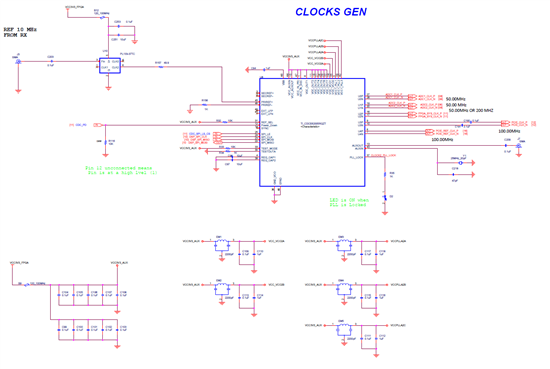

We designed a board with CDCE62005 as shown in the attached files. our input is 10 MHz sinusoidal that is converted to square using PL133-37TC. We also have on board 25 MHz crystal.

we programmed the CDCE with the attached .ini file. using the CDCE62005 EVM GUI (1.4.8). The problem is that we are not always getting pll lock using the 10 MHz reference. we got lock few times only. we tried "Calibrate" button, but no luck. the other problem is that the AUX is not working too. we tried just to pass the AUX to OUT and we don't see it?

Can you see any problem in the design or the .ini settings?...thank you so much in advance!

Please see attached files.

Regards,

8662.CDCE62005.docx8015.CDCE62005.ini

Murad