Hi,

Let us describe our problem. We have a board with FPGA and external PLL which is LMK04906.

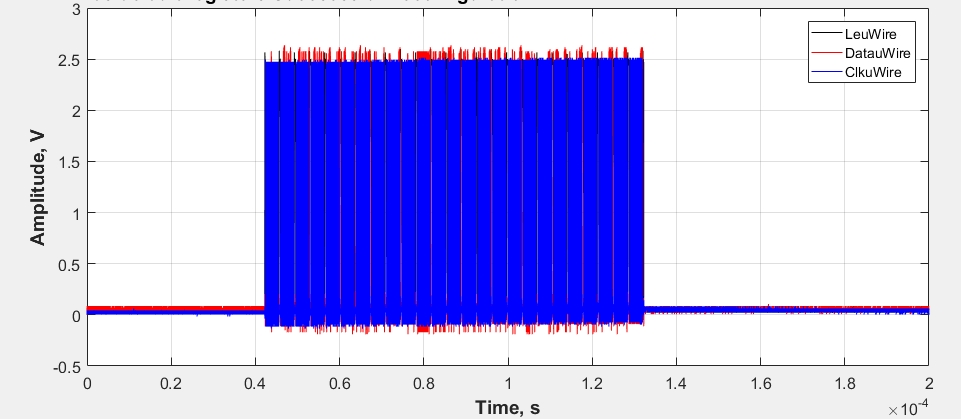

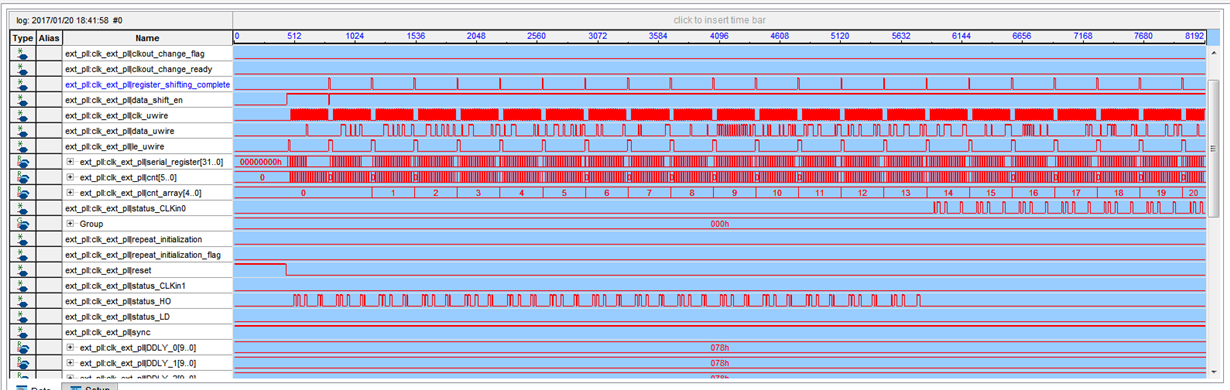

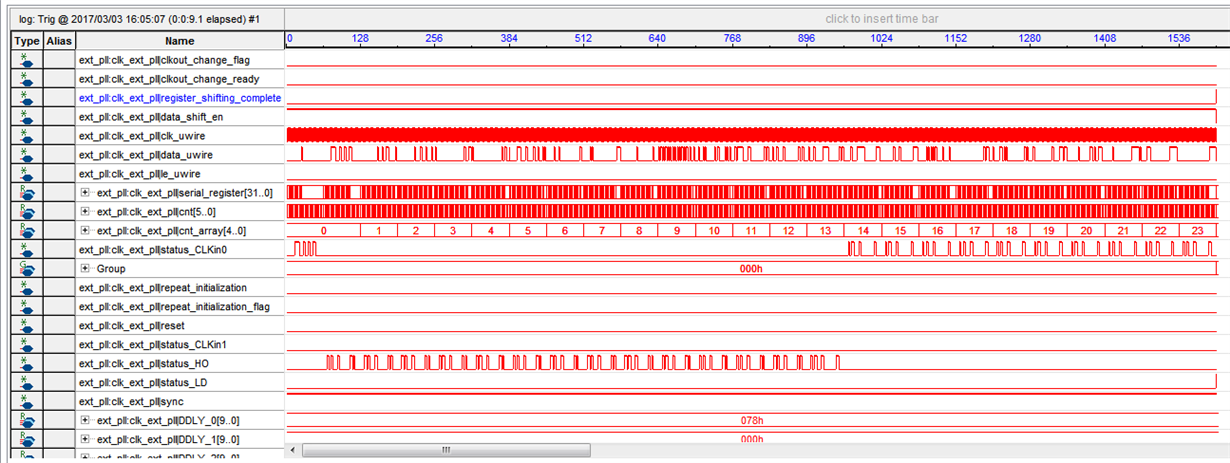

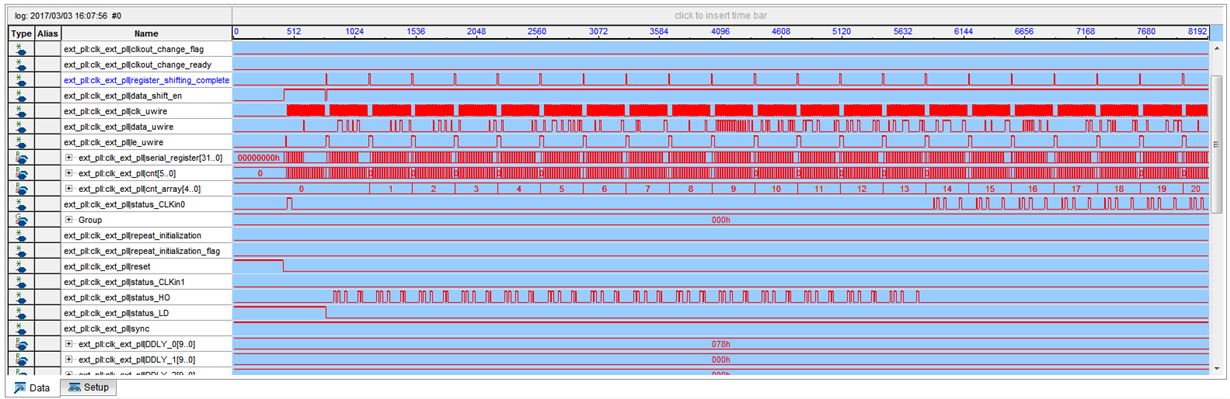

We observe some strange behaviour during initialization phase of LMK04906. After power up, we have reset registers that are default for LMK04906. After power-up, FPGA enter User Mode and initializate external PLL (using LeuWire interface). External PLL configures successfully (we program PLL to work in single PLL2 Mode with internal VCO and choose proper output clocks, Phase Detector and other settings). It also configures successfully after powerup start from external flash. It also successfully reconfigures an infinite number of times from User Mode if we initiate that initialization from PC-JTAG interface. But (!!!) after reprogramming FPGA (without cold reset) with the same programming file with the same settings PLL initializes wrongly (!!!!!). It means that - 1. PLL didn't reset 2. All registers from 1 to 31 didn't change their values, except register 30, which rewrites wrongly! (As we think, PLL after reconfiguration is insensible to rewrite registers R0-R29). That means that we are unable to reset PLL, because R0 value didn't chage.

Also interesting thing is that if we even readback from PLL after first initialization and reprogram FPGA, then PLL initializes properly.

Please help us with that issue!

Thank you very much in advance.

Best Regards,

Ivan