Hi Team,

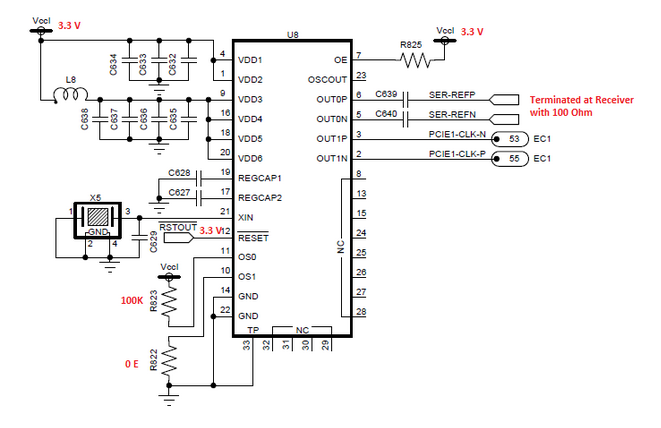

CDCM9102 device is being used at my customer in an application for 100 MHz clock generation (from 25 MHz crystal) . However, we are not observing any output. The other output is not terminated with 100 Ohm. Will this create any issue on the other output?

Please find below the schematic section. Kindly request your suggestion to resolve the issue. Thanks.

Best Regards,

Suhas R C