Hi,

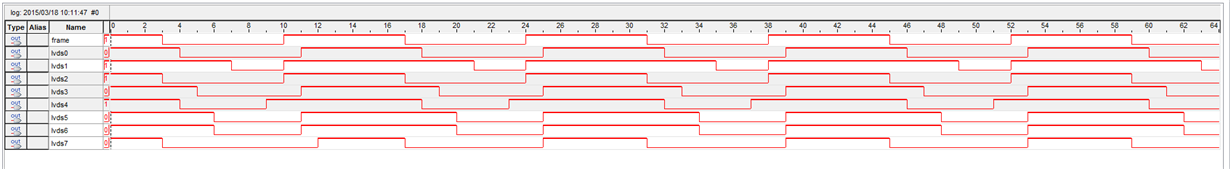

I’m working with the AFE5809EVM and I have some issues with LVDS output interface. I’m trying to deserialize 14-bits data of 8-channels configured in test pattern mode with a Cyclone V but I have lots of reading errors.

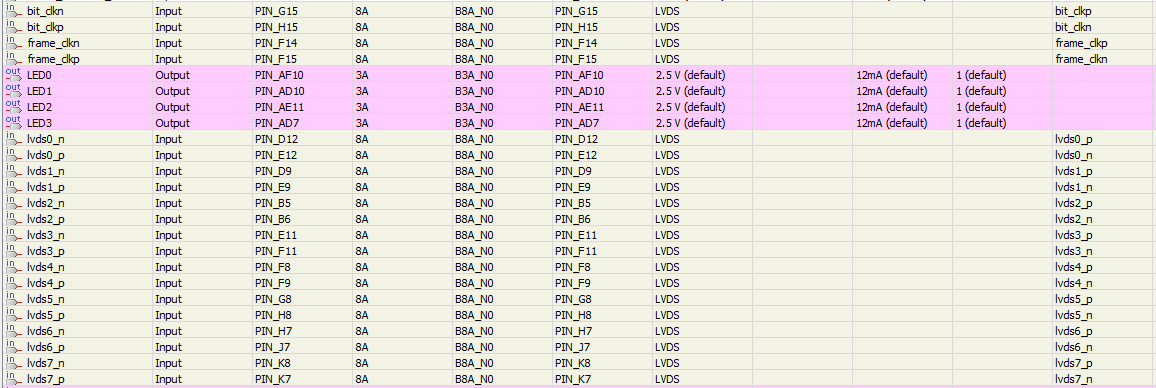

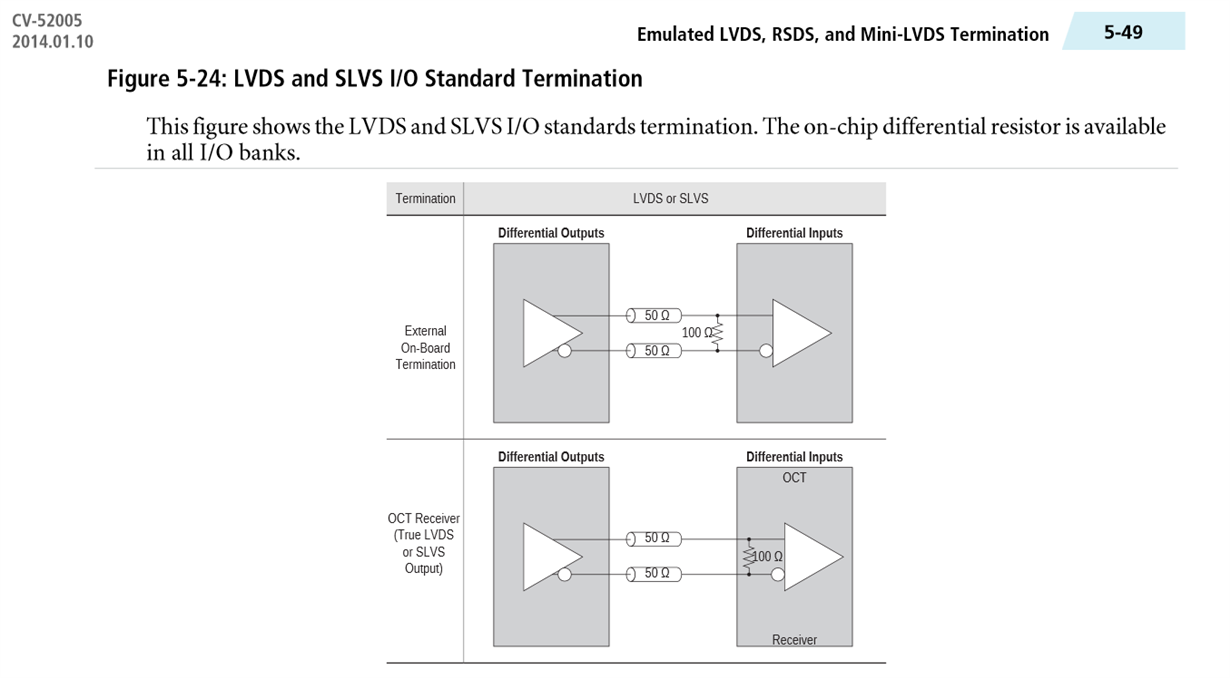

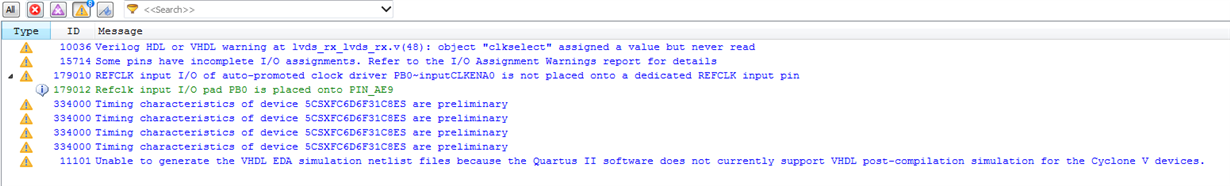

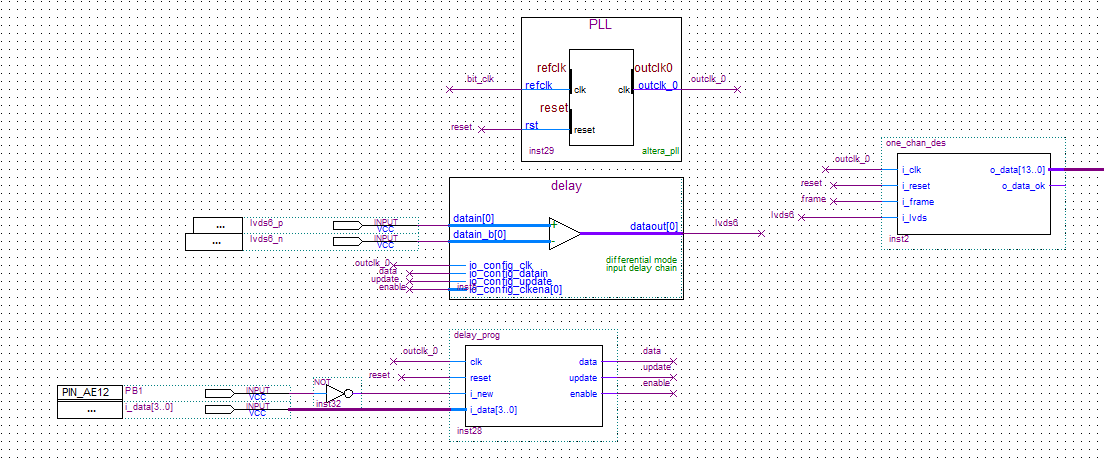

I’m using an interconnection board HSMC-ADC-Bridge and a development board SocKit as is shown in Fig. 1 and AFE5809EVM is in default configuration (with on-board CMOS clock on). In the FPGA, the SERDES module is configured by an Altera megafunction IP core named ALTLVDS_RX (see Fig. 2 ). This module needs a read clock and the 8-lines of serialized data and performs a 7-bits deserialization. I wrote a program in order to concatenate this 8x7-bits data in 8x14-bits data and to do the bit alignment when AFE5809 generates a sync pattern. Furthermore, I have a second program to check if they are errors in the reading of a ramp pattern.

Fig. 1 - Evaluation boards used

Fig. 2 - schematic of algorithm implemented

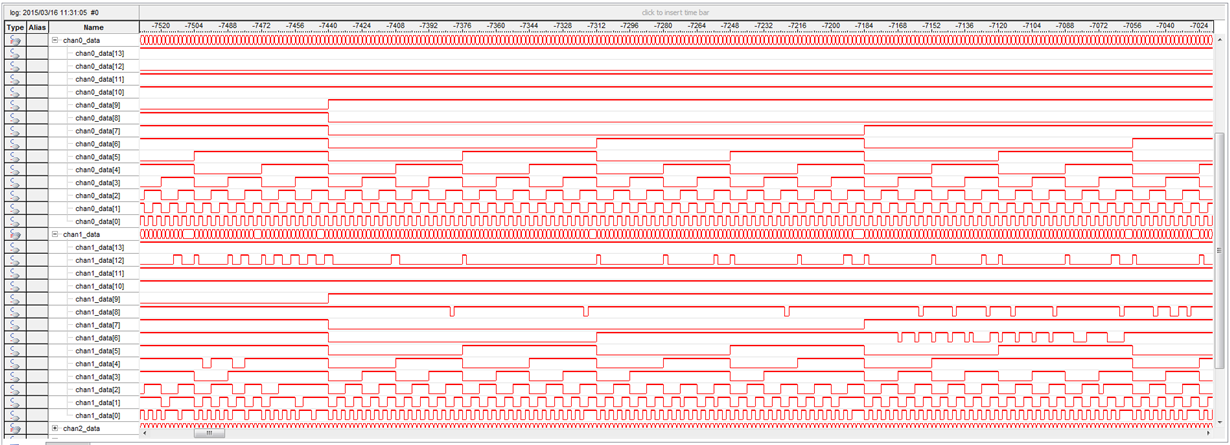

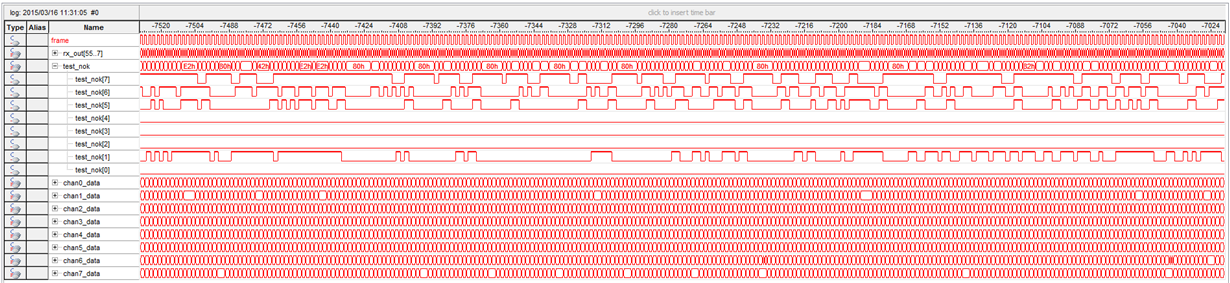

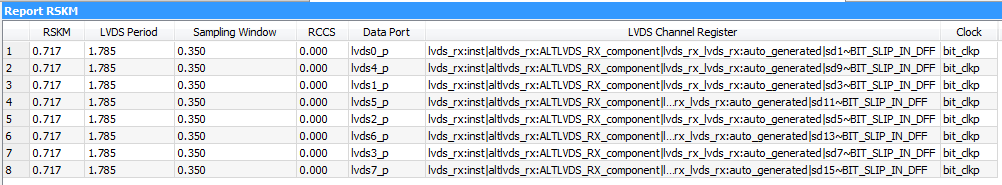

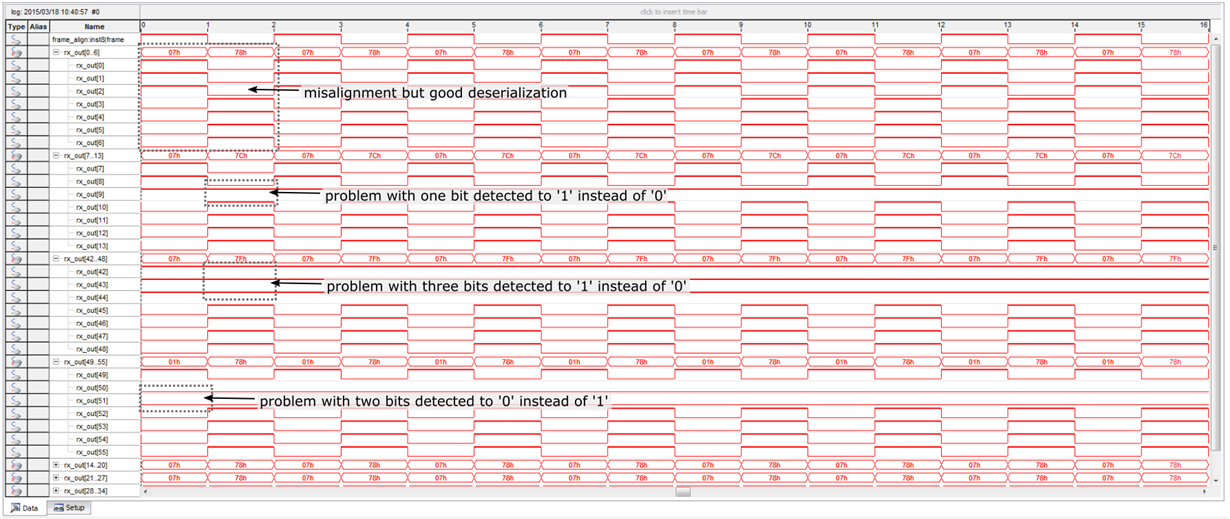

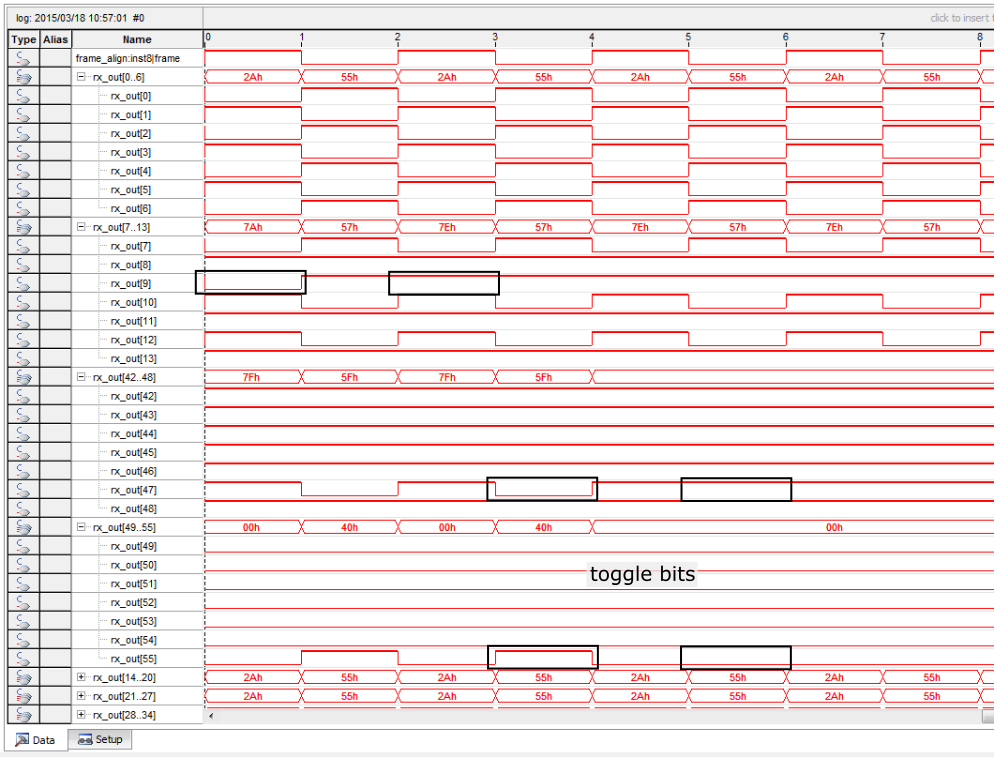

The Fig.3 shown deserialized data when AFE5809 generates a sync pattern. We can see that some channels output data aren’t stable (one or more bits toggle) and we have the good value only for 4 channels (3F80 in hexadecimal). In the Fig. 4, we can see the result of a “good” deserialization for the channel 0 and a “wrong” deserialization for the channel 1 during a ramp pattern. In the Fig. 5, we can see a marker of a goog deserialization (test_nok) which stay at level '0' when there is no problem (it's good for channel 0, 2, 3 and 4).

Fig. 3 - 8-chan deserialization of sync pattern

Fig. 4 - 2-chan deserialization of ramp pattern

Fig. 5 - test_nok marker with a 8-chan deserialization of ramp pattern

I don’t know where these errors come from but I have tried to visualize the output data lines of AFE5809 and I saw an oscillation in phase with the bit clock (representing by a gray line in the Fig 6.), which may be the source of the problem.

Thank you in advance for your support.