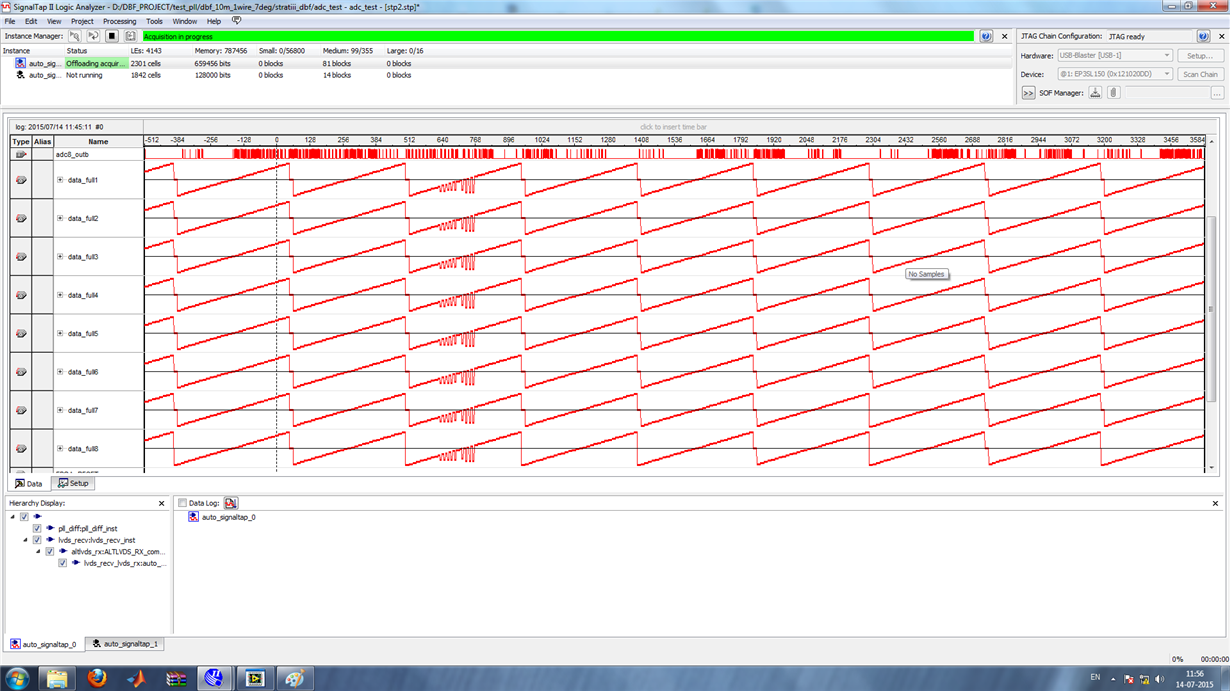

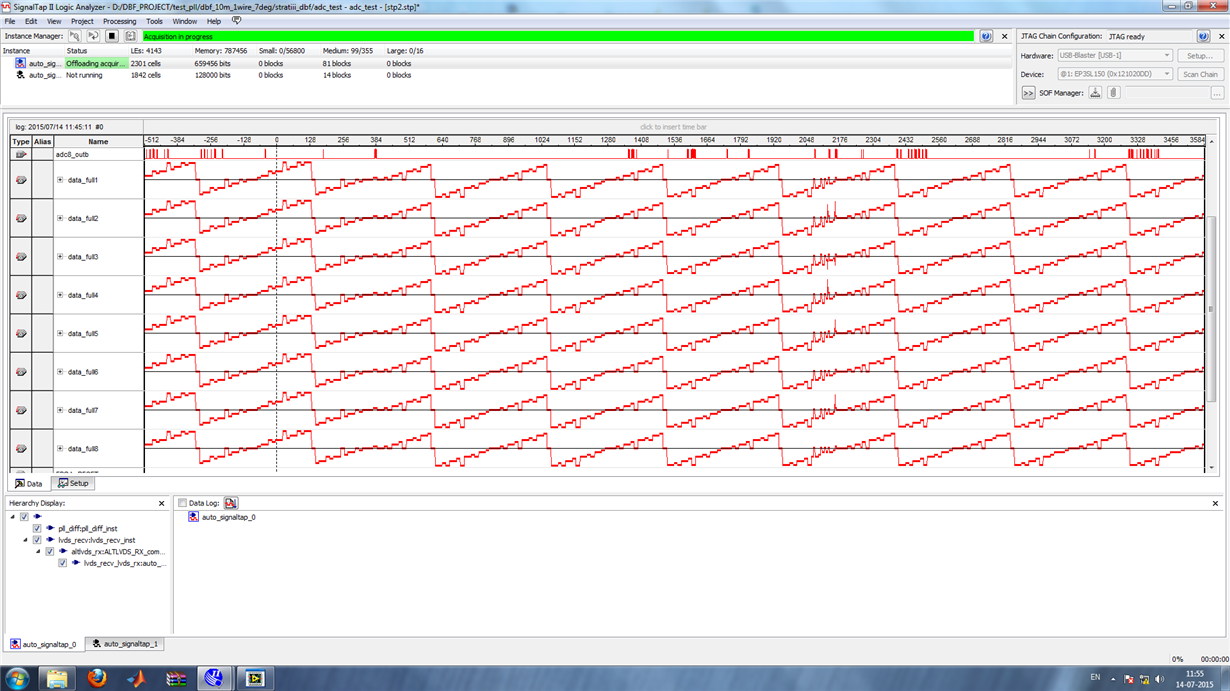

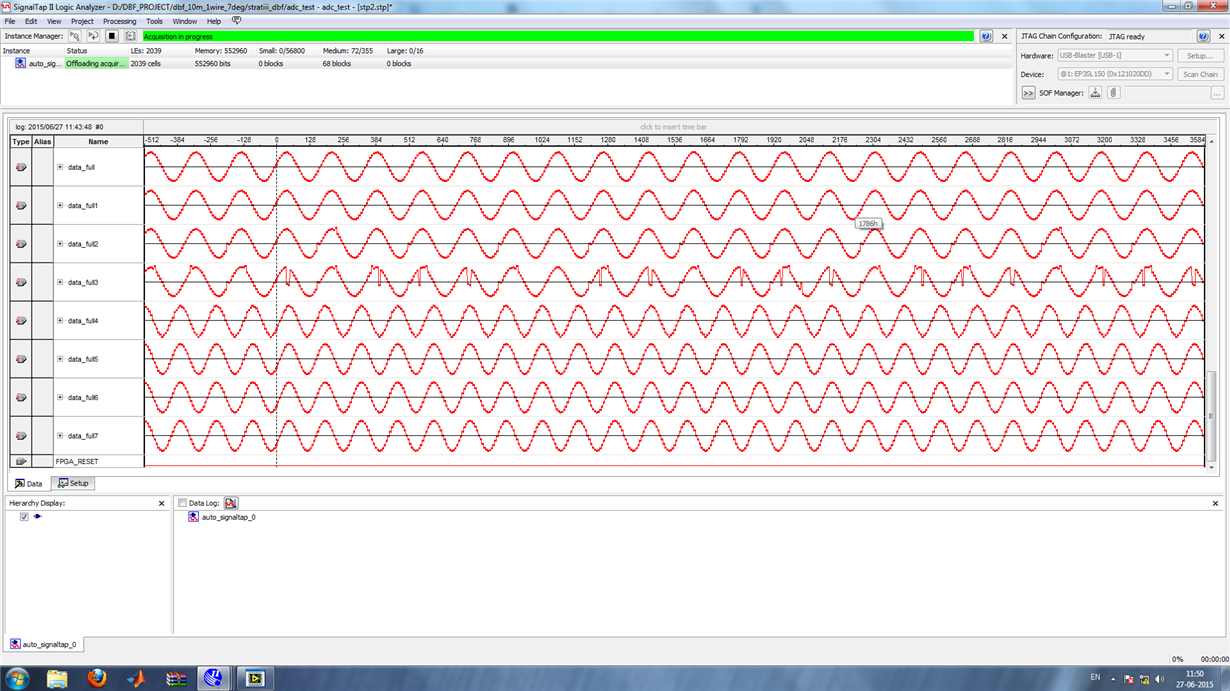

I need to interface ADS5294 EVM to ALTERA FPGA development board. I'm using Stratix III development board. With the help of HSMC-ADC-BRIDGE, i interfaced ADS5294EVM with STRATIX III board on HSMC port A. Whereas i'm controlling ADS5294 EVM through USB with the help of GUI. So, if i test some test patterns susch as sync,deskew, ramp or custom pattern on adc channel outputs for a 2-wire interface (default setup on an ADS5294 EVM), channel b outputs are not at all toggling for few channels and at the same time, i'm not getting proper pattern. How to resolve the issue. What is the recommended guidelines to use EVM with FPGA board?