We are facing issues with ADC10D1500CUIT. There are 2 ADCs on a single board which are used for Gain and Phase measurements. In the arrangement, ADC1 - ADC2 are synchronized using autosynch feature.

Each ADC receives two analog signals and a clock of 1350 MHz connected in 1:2 De-mux mode.

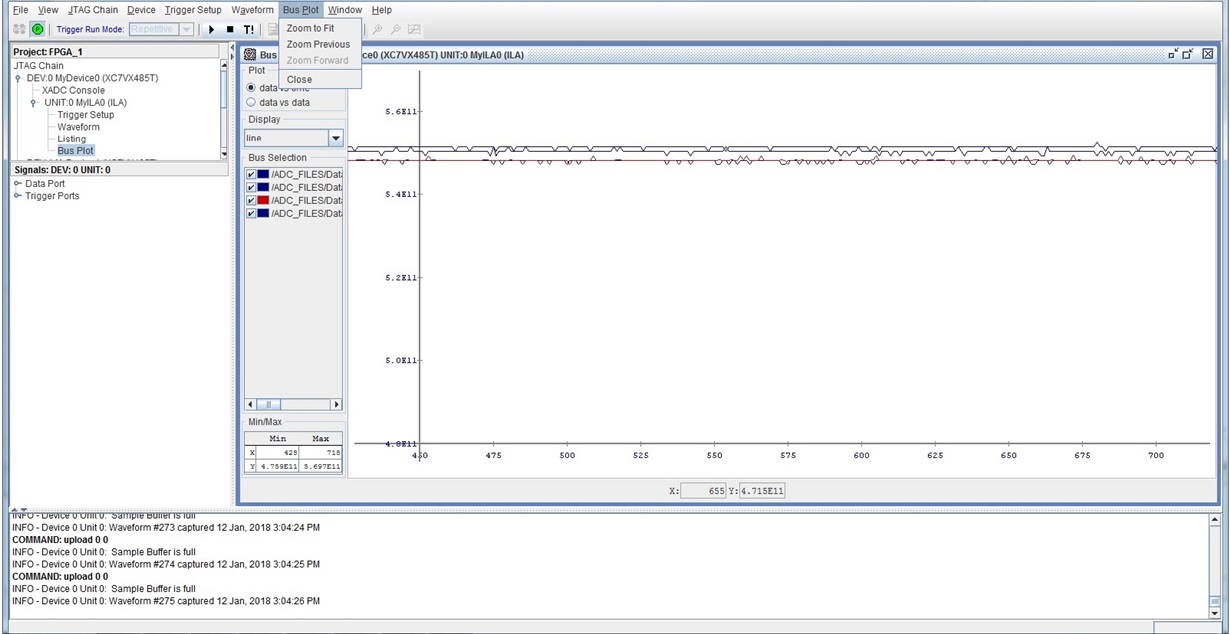

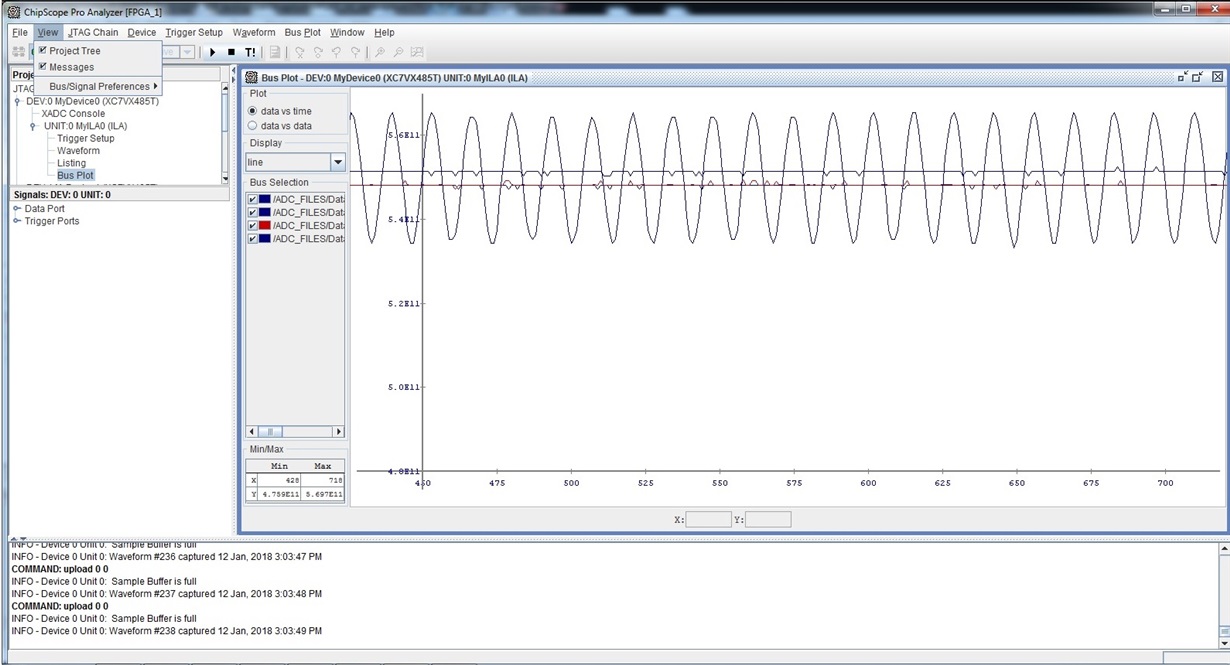

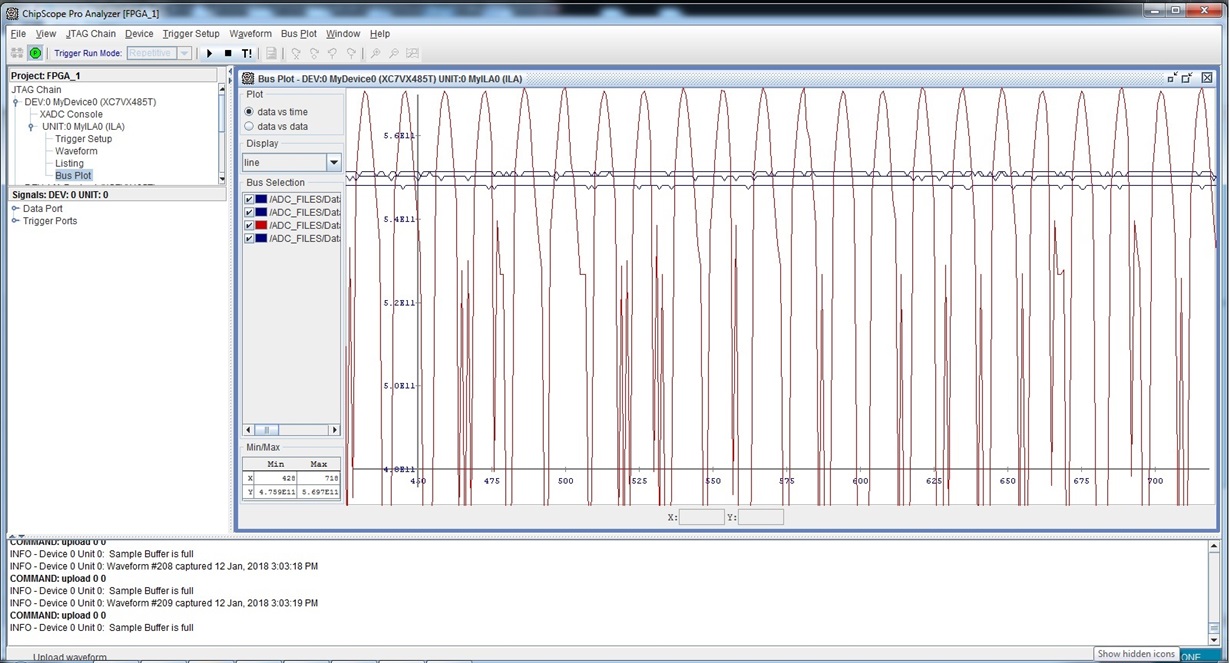

In some of the cards, we are facing issue with Signal Gain. We are applying the signal from same source to all channels of ADC’s (1GHz, 0 dBm to -40dBm).

In Higher Amplitude, Signal Level among all channels looks fine. But when signal level decrease, one of the channel (either ch-3 or ch-4) level shows higher level. Most of the time level will not decrease as per input below -16dBm.

We have checked input circuits, Baluns, and Clock Circuits. They looks fine.

Register Setting of the ADC's are as below:

CONFIG_REG[0] <= 24'h400000;/

CONFIG_REG[1] <= 24'h422A00;

CONFIG_REG[2] <= 24'h440000;

CONFIG_REG[3] <= 24'h467FFF;

CONFIG_REG[4] <= 24'h48DA7F;

CONFIG_REG[5] <= 24'h4A0000;

CONFIG_REG[6] <= 24'h4C1C70;

CONFIG_REG[7] <= 24'h4E0000;

CONFIG_REG[8] <= 24'h500000;

CONFIG_REG[9] <= 24'h520000;

CONFIG_REG[10] <= 24'h540000;

CONFIG_REG[11] <= 24'h567FFF;

CONFIG_REG[12] <= 24'h580004;

CONFIG_REG[13] <= 24'h5A0000;

CONFIG_REG[14] <= 24'h5C0001;//e master

CONFIG_REG[0] <= 24'h400000;

CONFIG_REG[1] <= 24'h422A00;

CONFIG_REG[2] <= 24'h440000;

CONFIG_REG[3] <= 24'h467FFF;

CONFIG_REG[4] <= 24'h48DA7F;

CONFIG_REG[5] <= 24'h4A0000;

CONFIG_REG[6] <= 24'h4C1C70;

CONFIG_REG[7] <= 24'h4E0000;

CONFIG_REG[8] <= 24'h500000;

CONFIG_REG[9] <= 24'h520000;

CONFIG_REG[10] <= 24'h540000;

CONFIG_REG[11] <= 24'h567FFF;

CONFIG_REG[12] <= 24'h580004;

CONFIG_REG[13] <= 24'h5A0000;

CONFIG_REG[14] <= 24'h5C000F;//e slave

Please let us know what might be the reason for this mis-behaviour. How we can rectify this issue.