Other Parts Discussed in Thread: DAC34SH84, LMK04808

Hello,

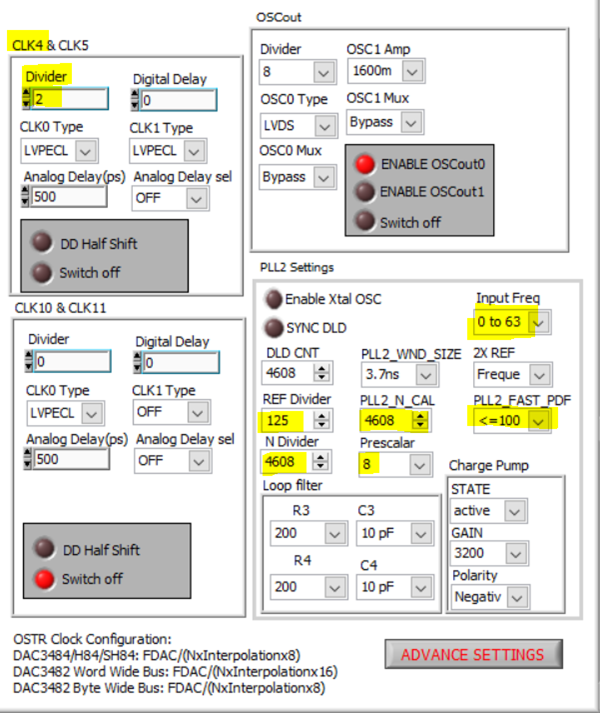

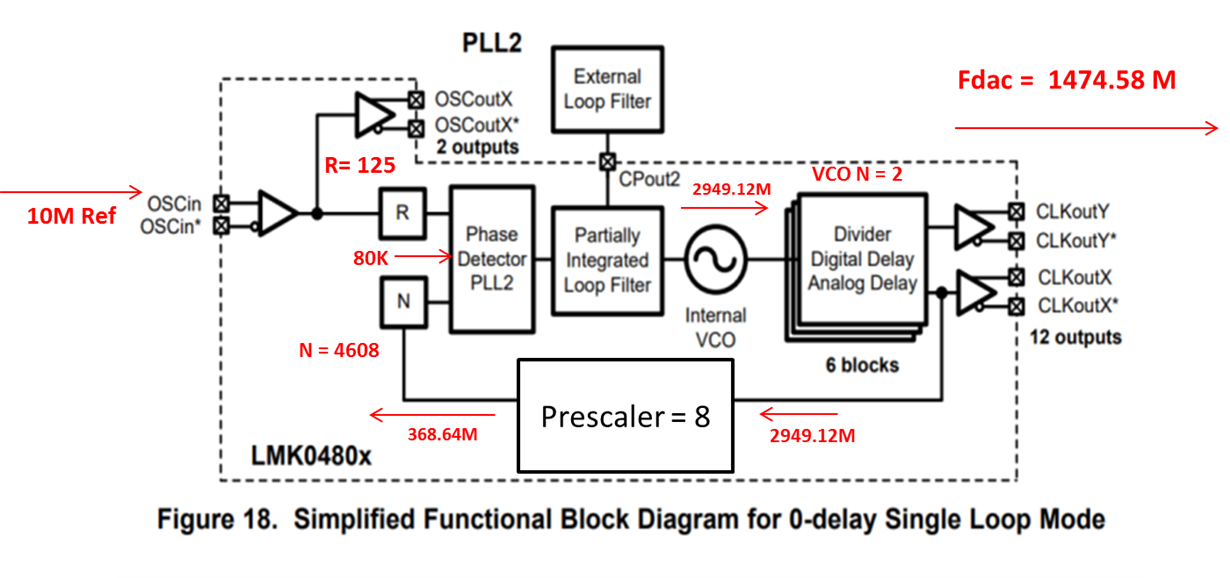

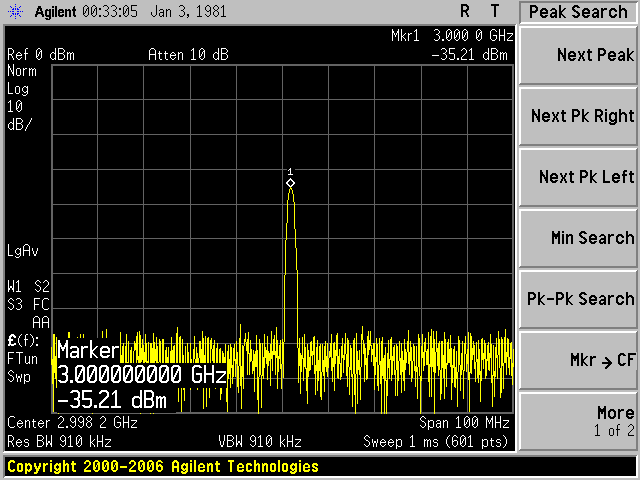

I am currently trying to use the PLL settings on the TSW30SH84EVM to control the DAC clock frequency and I am having issues following the example in the reference manual. I was wondering if there is anyway I could receive some guidance to using this setting in the TSW308x gui to control the DAC clock frequency and the data rate in the high speed data converter pro? Even if its just a configuration file that uses the PLL setting to set the DAC clock frequency that would be very helpful. I am also curious if I can use this PLL setting to set any data rate of my choosing to be used with the TSW1400EVM?

Thanks,

Joshua Johnson