Dear Specialists,

My customer is considering ADS8326 and has questions about timing spec.

I would be grateful if you could advise.

---

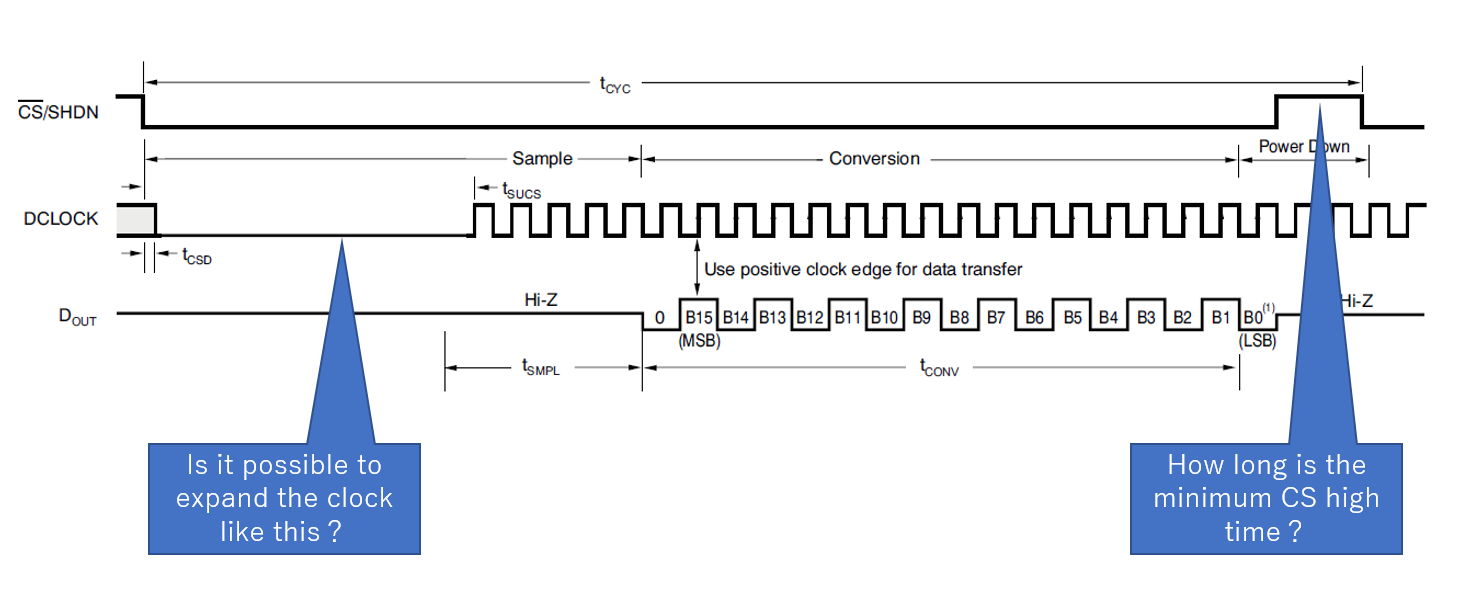

Could you please see the figure and answer these questions.

(1) Is it possible to expand the Dclock?

(2)How much is the minimum CS high time?

---

I appreciate your great help in advance.

Best regards,

Shinichi