Other Parts Discussed in Thread: TINA-TI, , LMK04828

Tool/software: TINA-TI or Spice Models

Dear Sirs,

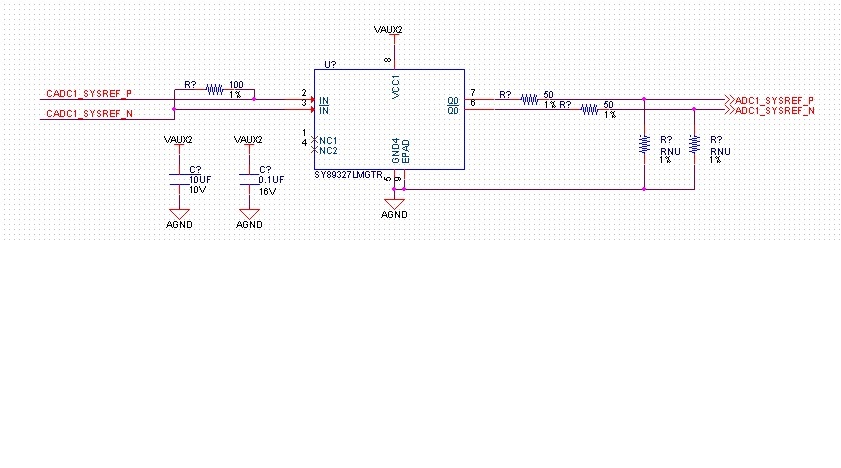

I'm designing a board that uses two ADC12DL3200 connected at one FPGA Xilinx.

The FPGA downloads the data and drives the ADC12DL3200 control signals.

For example the SYSREF signal is driven by a LVDS FPAG Output.

Is it correct?

Is it possible to drive the SYSREF input signal with a LVDS driver (FPGA output)?

I'm looking forward to hearing from you.

Best Regards,

Daniele Sassaroli