Hi,

my customer is currently working on a design with ADS7853 and they have a concern.

First they set the configuration register for 16-bit mode, 2 data lines, etc Data: “1000_1010_0001_0000”

Clock frequency is 2.5 MHz for testing, started at 10 Mhz and that is what they are going to use in their product.

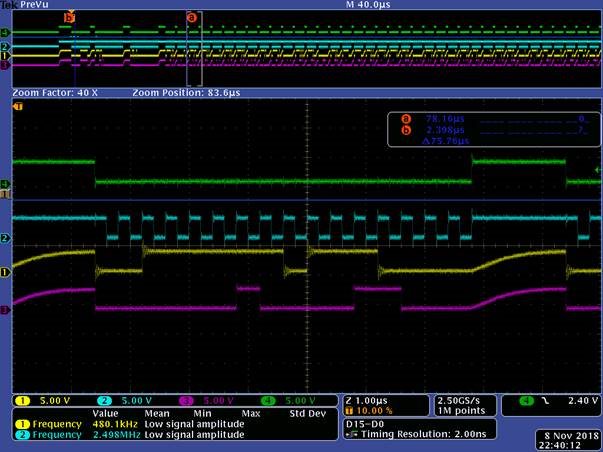

Green: CS_n

Digital 1: SDI

Blue: SCLK

Yellow: SDOA

Purple: SDOB

Next they init a readout of the configured values:

Then they read the configured values(here it is obvious that the output data is launched on the falling edge of sclk):

Finally they entered “runtime” where the values are read often.

Here you can see that the data is launched on the rising edge of the sclk. The datasheet states that the data should be launched on falling edge.

See page 42 and 43 in the datasheet. D11 should be put out on the second falling sclk after cs_n has gone low.

I can’t find anywhere in the datasheet that data should be launched on the rising edge, however on page 41 it looks like it in the diagram but the text and table says falling edge.

could you please help us here.

regards,

Stani