Hello,

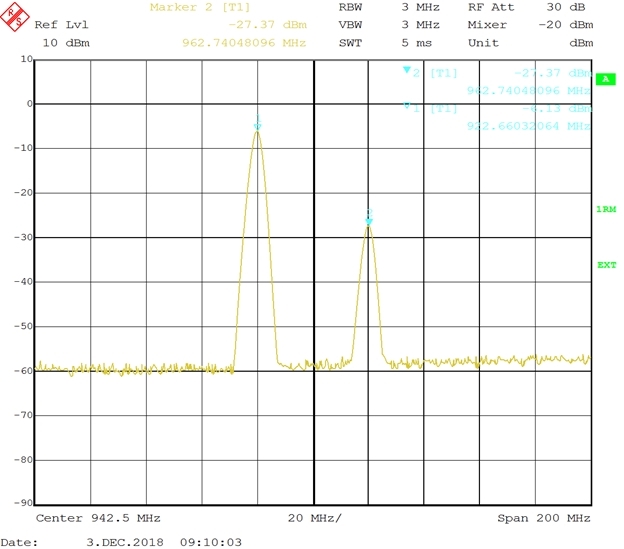

we do sometimes observe mirror signals (mirrored to the NCO) on our DAC output.

Please see the attached screenshot.

After initialization and JESD synchronization the mirror signal either stays available or not until the next initialization.

The DAC38RF83 is set to Interpolation 18; LMFSHd = 44210; 2 TX; 9 GHz DACCLK.

What could be the reason for this?

Our assumption is that one lane might be delayed. Perhaps wrong lane buffer setting during initialization.

And therefore I- and Q-data are delayed to each other.

How could this be double-checked? Is there a testmode in the DAC available to check the alignment of the lanes to each other?

Thank you in advance

Best regards

Christoph