Hello,

I have a confusion about the operation of the DDC114 Analog amplifier stage.

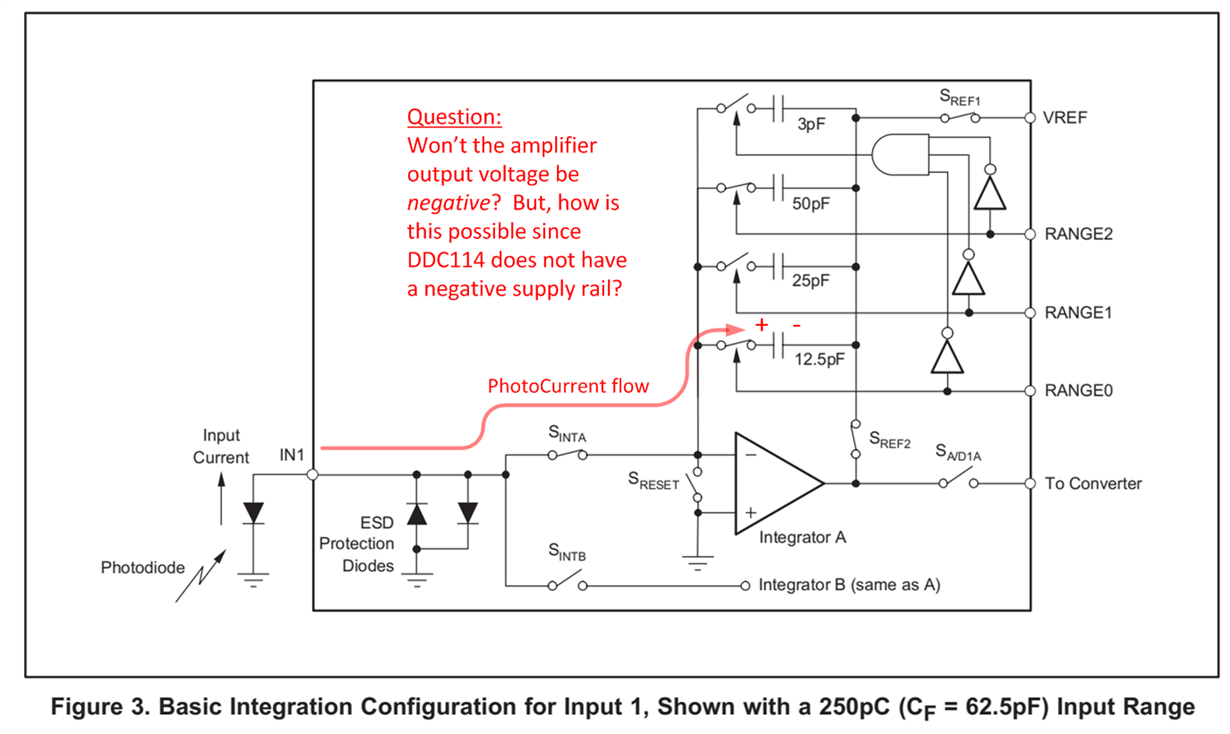

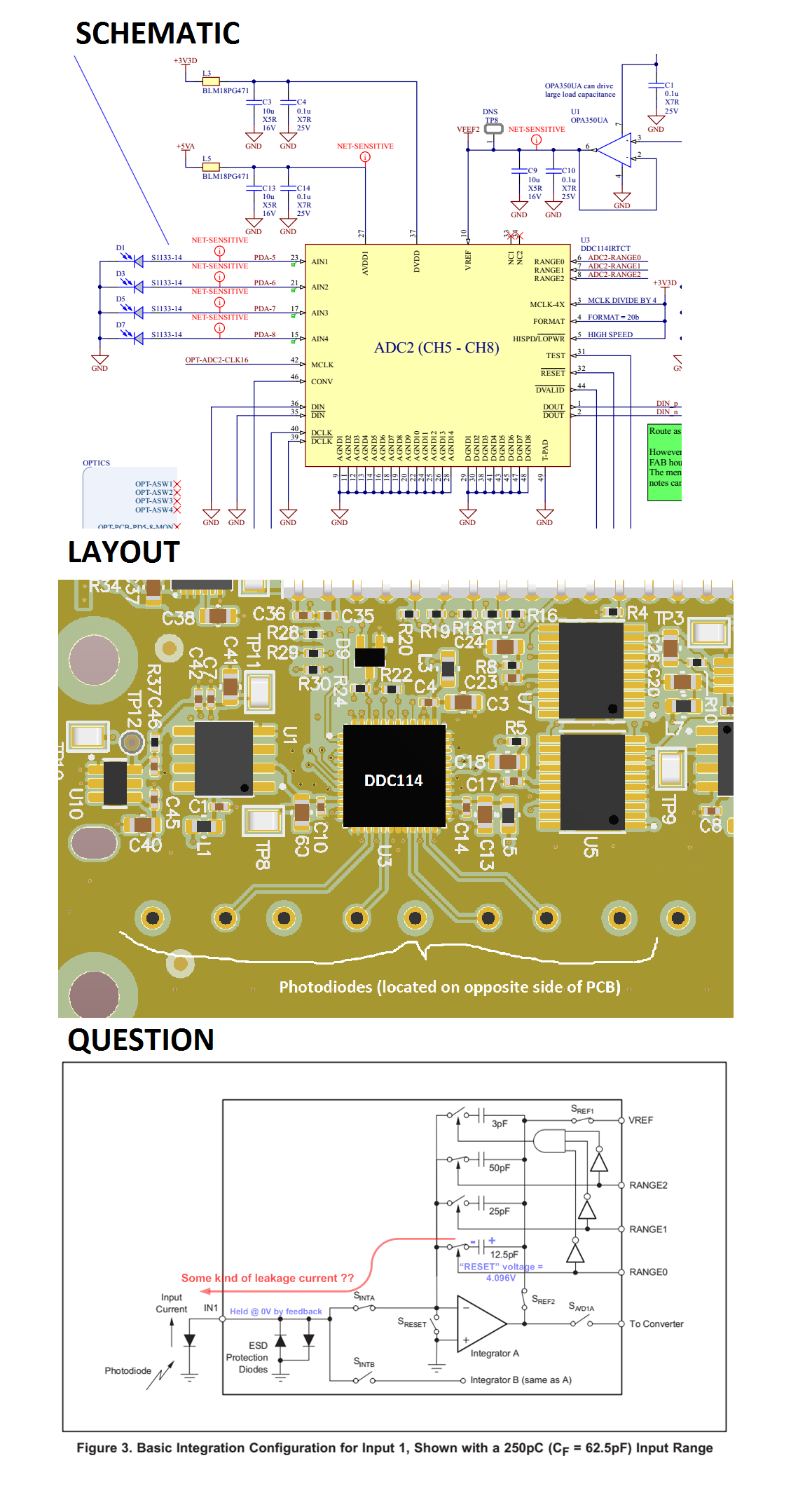

The datasheet shows the following circuit diagram for the input stage. I have added the red text markups.

If the photocurrent enters the amplifier in the direction shown, won't it charge up the capacitor such that the amplifier will output a negative voltage? However, there is no negative supply pin on this part. So I do not understand how this device can measure photocurrent flowing in the direction that is shown.

Please explain, and sorry if i am missing something obvious.... !