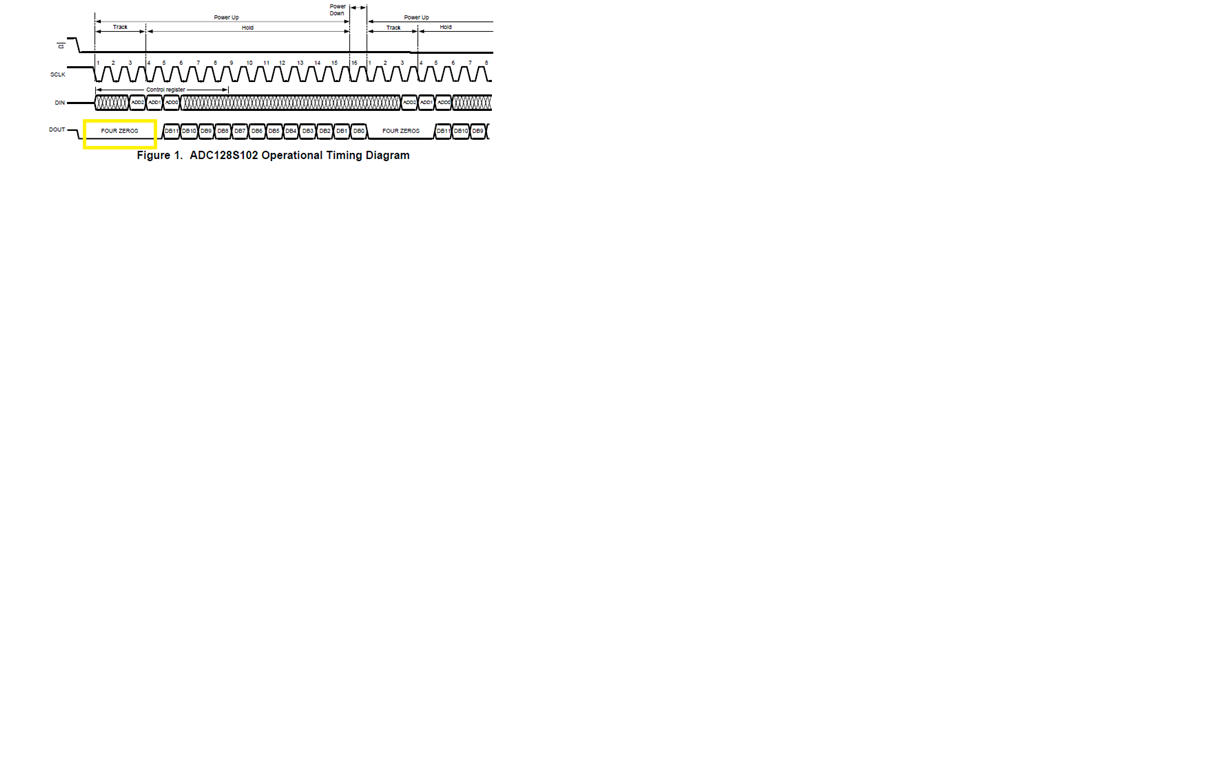

I am seeing something other than all zeros in first 4 bits of the "Data Out" serial data after the CS for the ADC128S102 is asserted.

Please see attached file which shows the timing from the data sheet. I highlighted in yellow where the 4 bits should be zero. The rest of the Data Out stream looks ok, i.e., the 12 bit ADC reading appears to be consistent with the voltage I presenting to the ADC.

I can provide more details, but I'm just hoping that someone has seen this before and recognizes the problem.