Other Parts Discussed in Thread: DAC37J82, , LMK04828

Hello, I'm attempting to establish a link between the DAC37J82 and a transmitter in an FPGA

Setup details :

- DAC37J82EVM board

- Xilinx VCU118 Demo board

- JESD204 v7.2.1 IP is instantiated

- JESD204B subclass 1

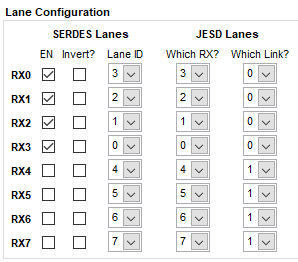

- LMFKS = 4, 2, 1, 30, 1

- 1 GSPS sampling rate, 250 MHz core clock, 10 Gbps line rate

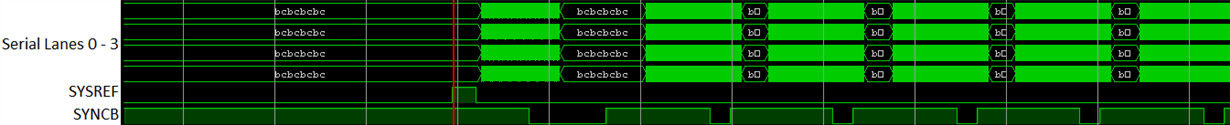

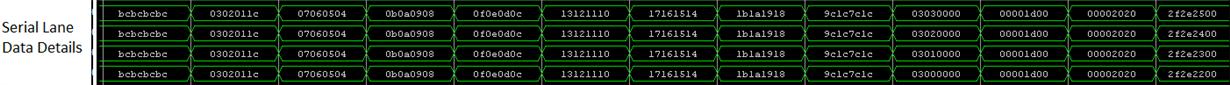

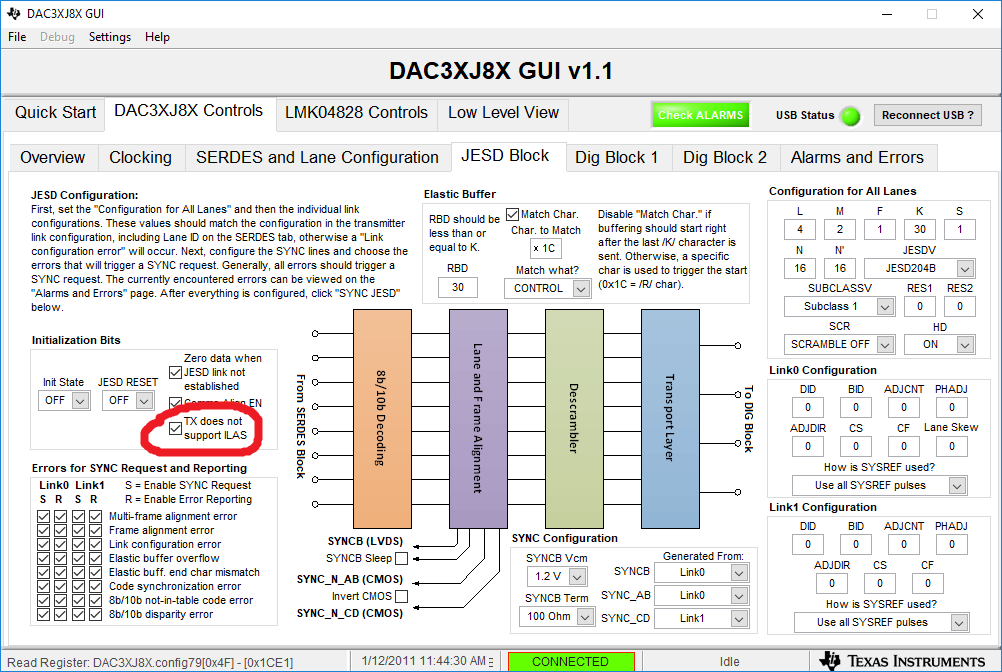

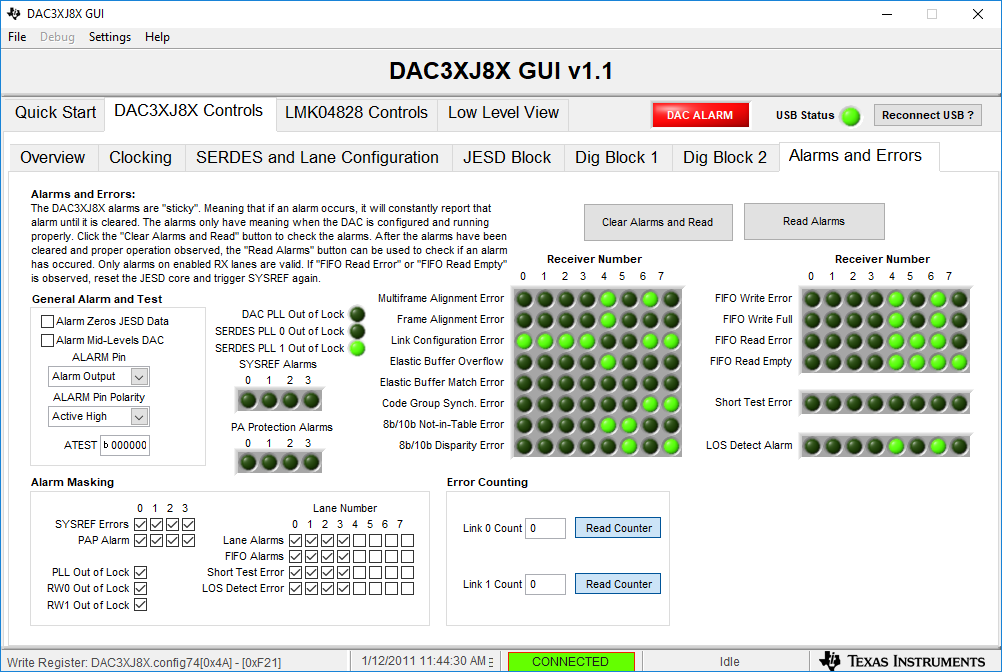

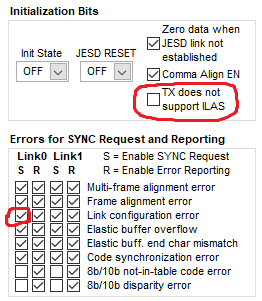

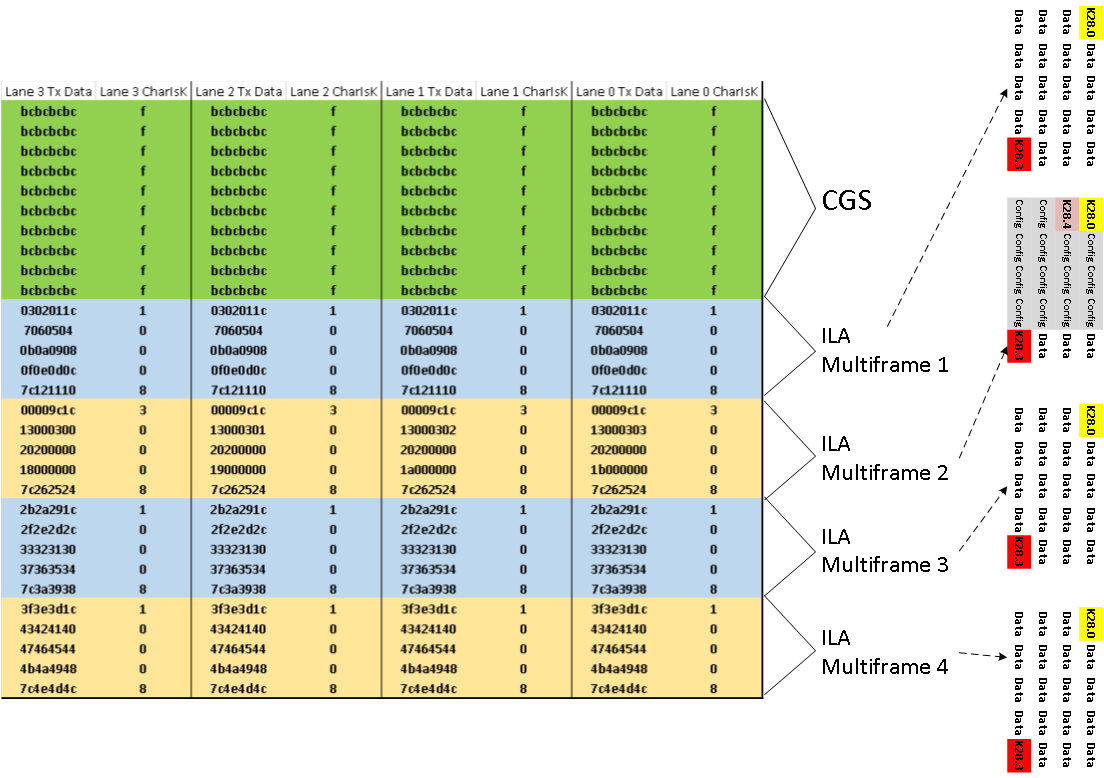

I've followed the setup steps on page 107 of the DAC37J82 datasheet and when I trigger SYSREF from the LMK04828 on the DAC EVM, I see that SYNCB line from the DAC toggles between asserted and deasserted indefinitely. I'm not quite sure why this is since the ILA sequence being output by the FPGA looks good as far as I can tell.While in this state, the DAC EVM GUI reports a lane configuration error for lanes 0 - 3.

If I check the 'Tx does not support ILAs' box in the DAC EVM GUI, things seem to work a lot better. I can verify on a spectrum analyzer that my 374 MHz test tone generated in the FPGA is being properly output by the DAC.

Any help with figuring out why I the ILA sequence break the JESD link establishment would be greatly appreciated, thank you.