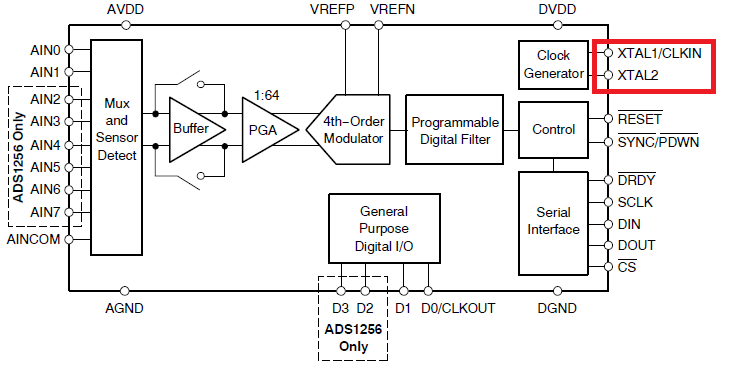

I have ADS1256 ADC module, which is interfaced with a STM32F746,

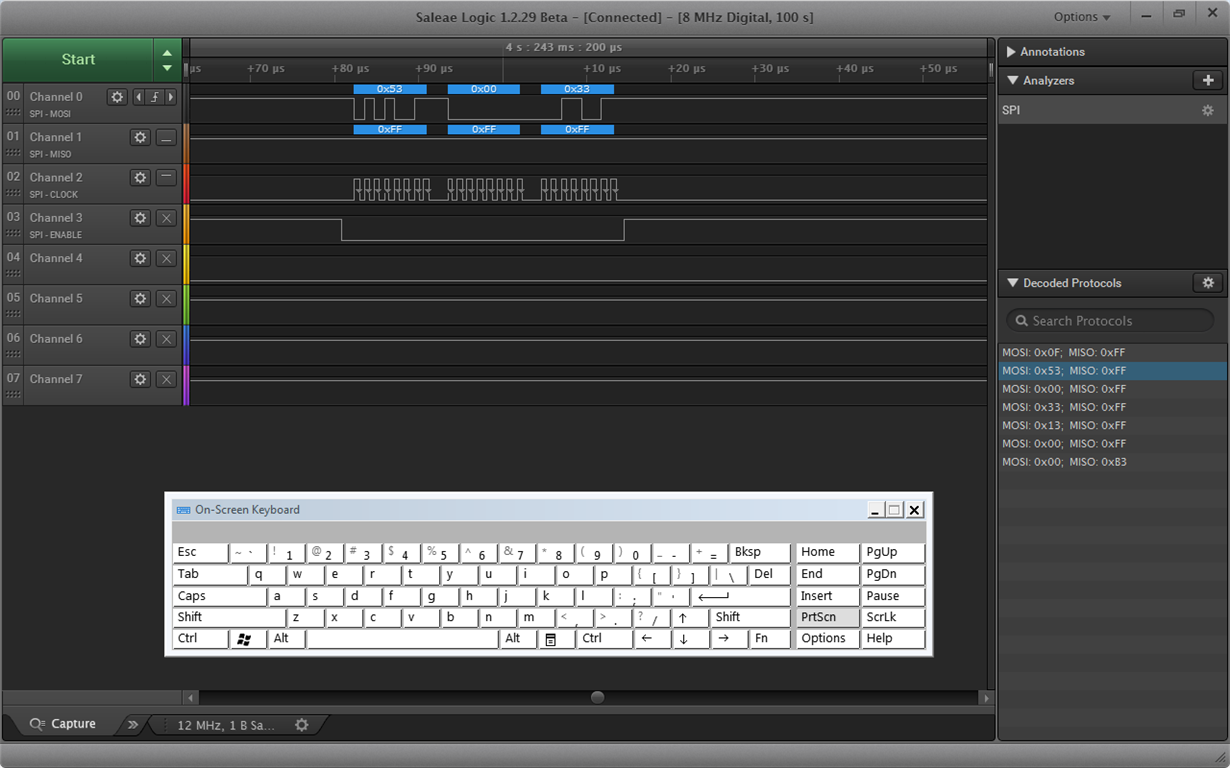

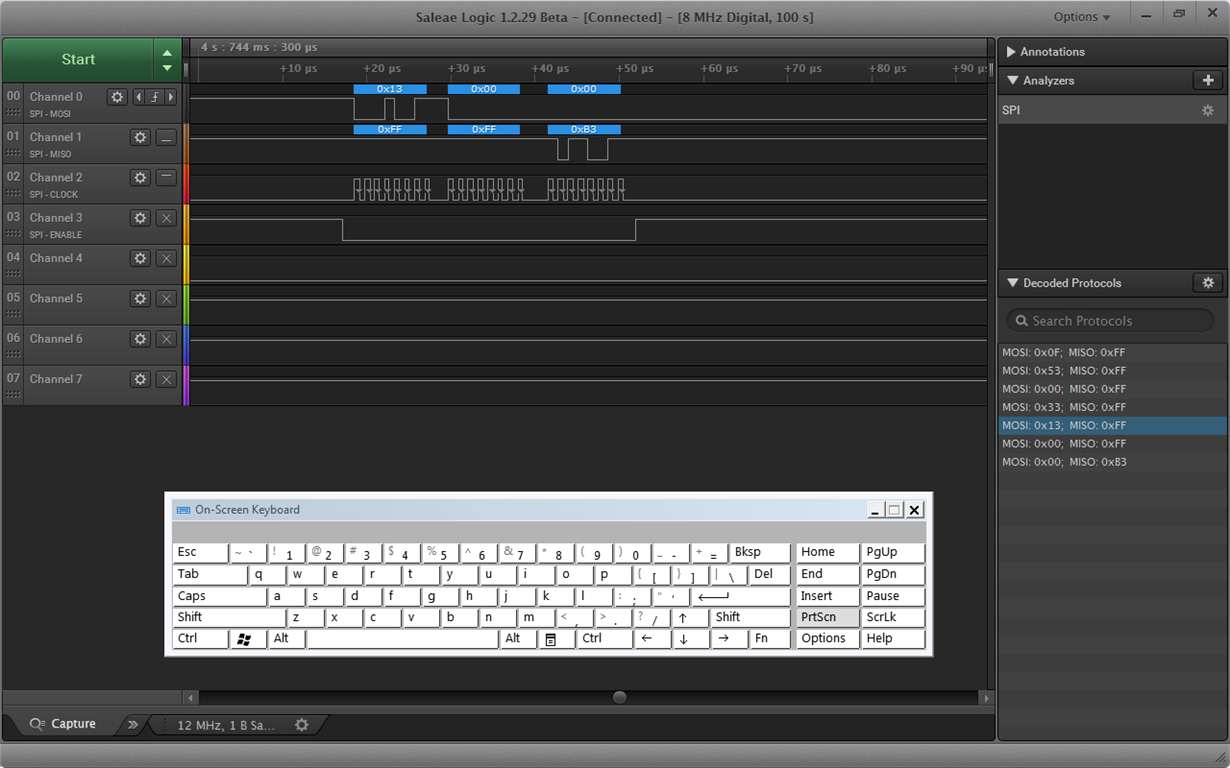

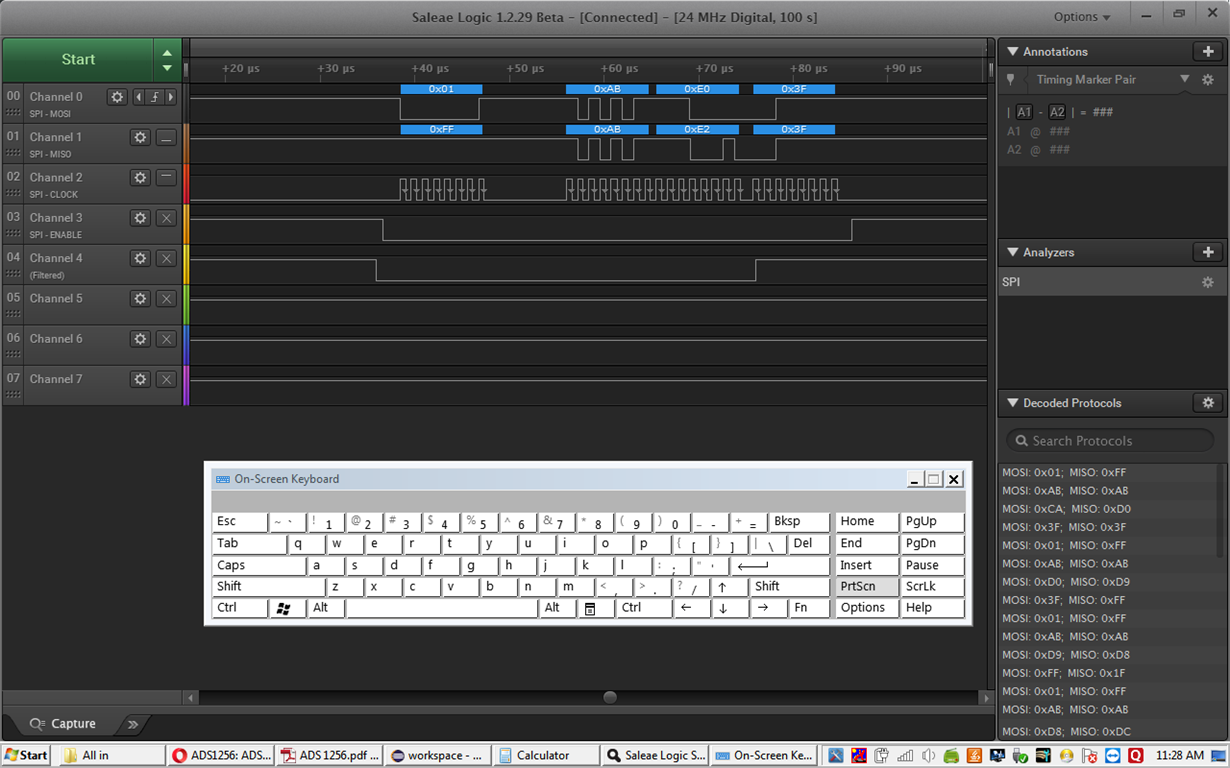

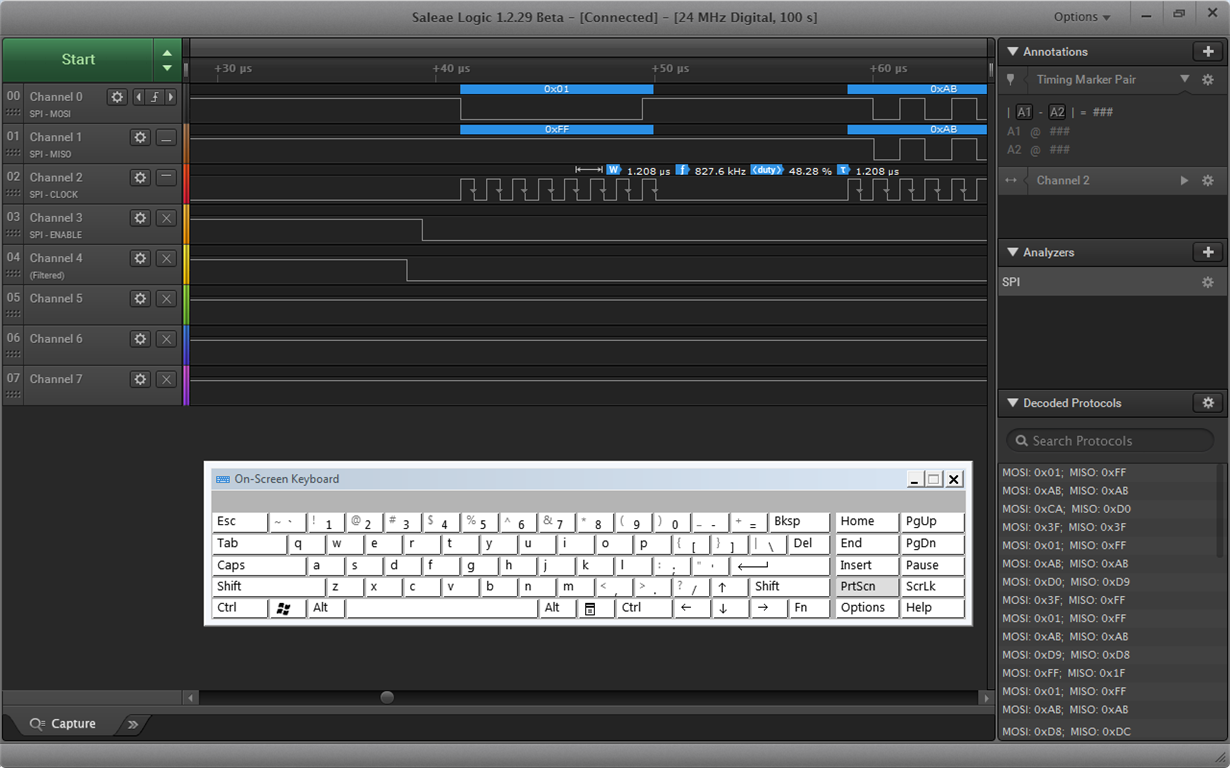

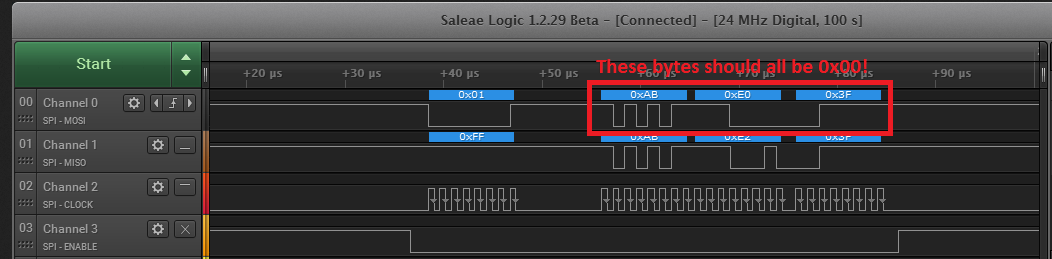

I stared with a Read Registers default values are ok as per data Sheet but when i write any value to any register MSB i.e bit7 is always '1' while reading,

for eg.

DRATE: A/D Data Rate (Address 03h)

if i write a 0x33 that is 00110011---15SPS

while reading i always get a 0xb3 that is 10110011,

similarly for all register read bit 7 is always '1'

please find the attached logic analyzer Screen shots

Thank you.