Other Parts Discussed in Thread: ADS42JB49, ADS54J60, ADS42JB69EVM

According the data datasheet in Page 35,

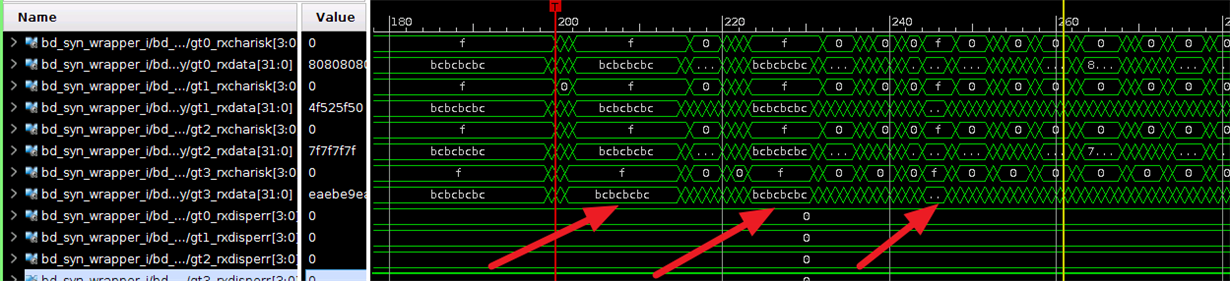

after sync is pull high, ILA sequence begin after K28.5, as shown green Ks. and then 4 K frames, followed by normal user data.

But this chip, 250Mhz, 4 lanes, 2.5Gbps, the ILA sequence is not compitable with the correct protocal.

a lot of K28.5 is inserted in this ILA progress.

We brought the newest EVM board, PCB Rev D.

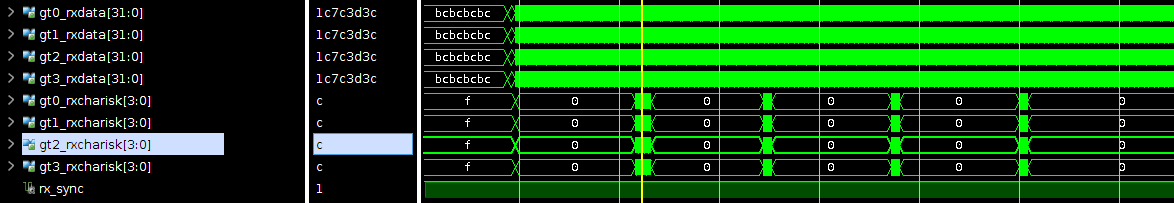

Besides, we tested the other chips, which exactly matchs TI ADS42JB49 datasheet, as below :

So how to solve this problem, to meet the datasheet, and JESD204B protocal?