Hi there, I am using the eval kit with an FPGA wired in as the master and am experiencing some trouble with the ADC not giving me data on the first DRDY falling edge. Then I don't see DRDY come back down low so I am wondering if I have a setting incorrect somewhere:

I have the following settings for asynchronous interrupt mode with +/-2.5V input voltage:

JP1: Installed to allow FPGA to be the master

I am using the USB power so left the JP2 and JP3 jumpers as is

JP5: 1-2: (M0: IOVDD Asynchronous interrupt mode)

JP6: 2-3 (M1 : GND 24 bit)

JP7: I tried both 2-3 and float and received same results. (M2 hamming code disable)

JP8: Uninstalled (Charge pump of)

JP9: Tried both installed and uninstalled. (use onboard reference)

JP10: Uninstalled (Use on board IOVDD)

JP11: 2-3 (Use +/-2.5V supplies)

I am using the following config process to enable the ADC for 4096 Oversampling to give me a 4KHZ sampling rate in asynchronous interrupt mode. Let me know if there is an incorrect setting in the CFG:

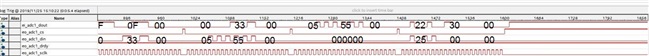

Send Null Command: 0x000000

Send Unlock Command: 0x065500

Send SYS_CFG_REG Write: 0x4B6800

Send CLK1_REG Write: 0x4D0000

Send CLK2_REG Write: 0x4D0000

Send ADC_EN Register Write: 0x4F0F00

Send Wakeup Command: 0x003300

Send Lock Register Command: 0x055500

Send Null Command: 0x000000 (I get every response up to here correct and you can see that in the logic analyzer shot)

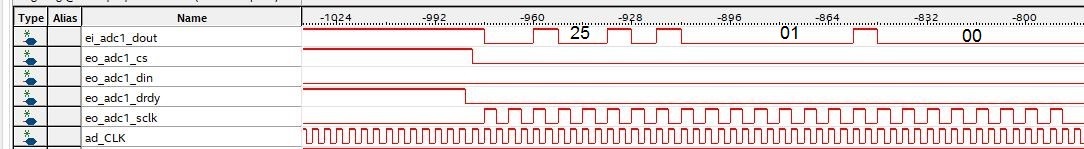

Wait until the ADC pulls DRDY low and then go and read all the channel data. When I read the data, I get the Lock register command back as the status but flatlined DIN for the 4 channels of data. When I keep the ADC as is and reset the FPGA to restart the initialization routine, I and only then see the correct data from the ADC after DRDY goes low. Then after this read, I don't see DRDY come back low again.

This is the initialization:

This is the first data read: