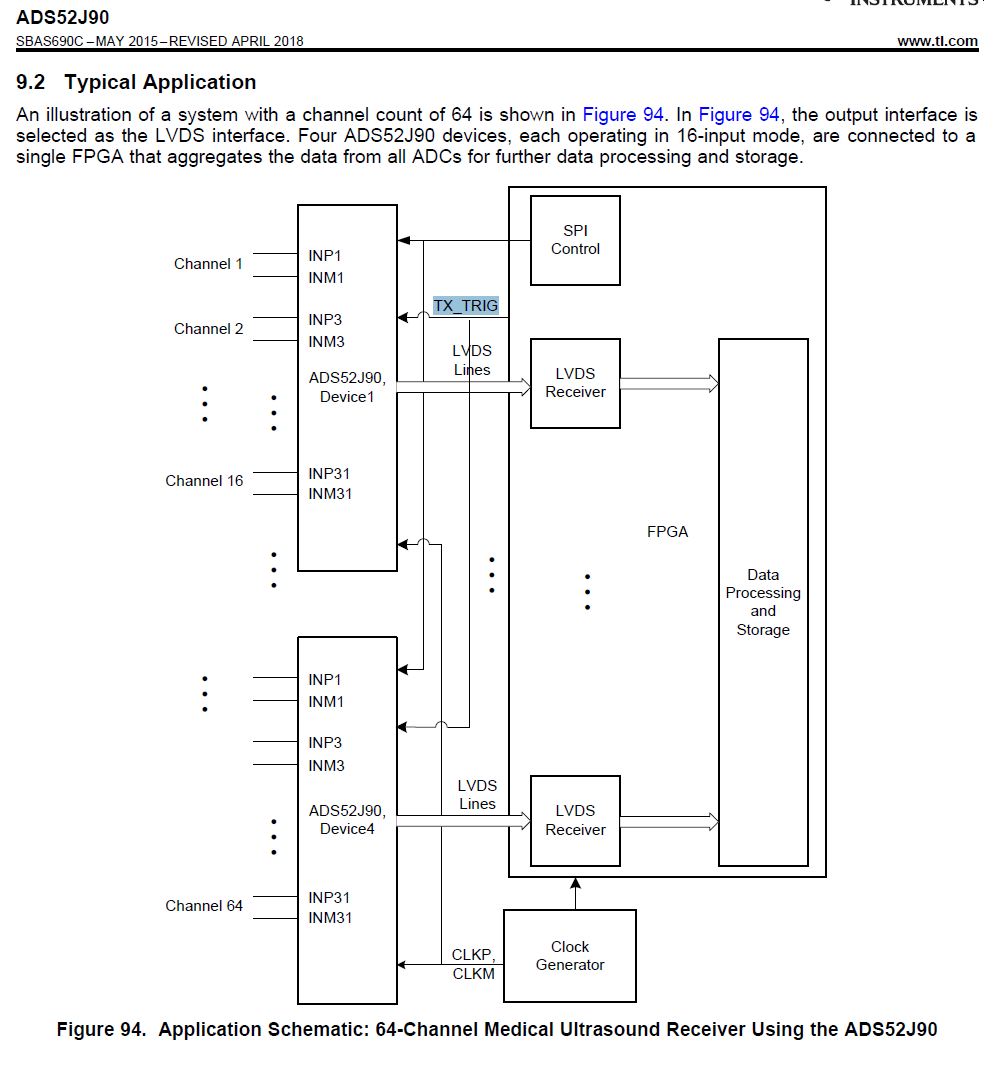

We want to use multiple ADS52J90 ADCs in parallel as shown in the figure 94 below. TX_TRIG should be a moderately clean signal because of the setup and hold timing requirements imposed on TX_TRIG. The signal integrity of TX_TRIG is uncertain because the design has multiple ADCs branching into several stubs. Do you have any guidance on how we should terminate TX_TRIG for acceptable signal integrity? For example, options might include "no termination" or "source-side termination" or "use a dedicated TX_TRIG signal for each ADC."

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.