Other Parts Discussed in Thread: DAC8775, ALLIGATOR, DAC8775EVM, LP38798

Hello,

I'm testing DAC8771 SPI communications before enabling/configuring any of the BBC arms (just AVDD=12.1V and enabling internal reference).

I select channel 0 (reg=0x03; data=0x0030) to disable the default daisy chain. Set reset configuration to enable internal reference (reg=0x2, data=0x0013).

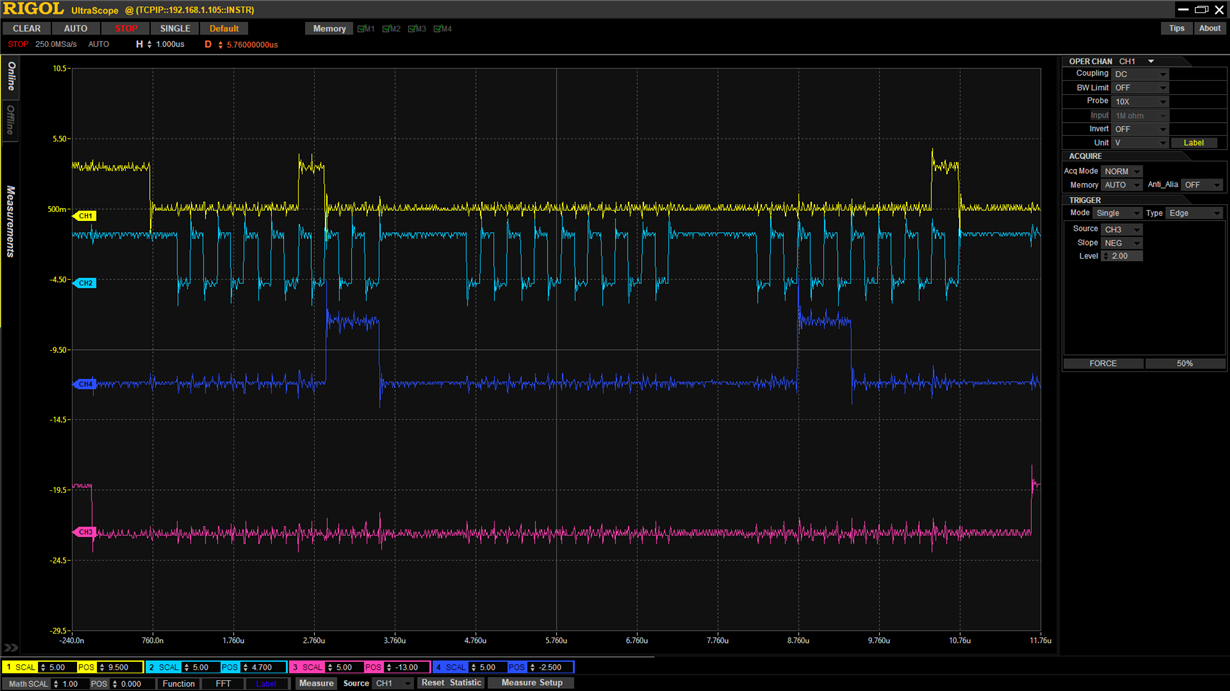

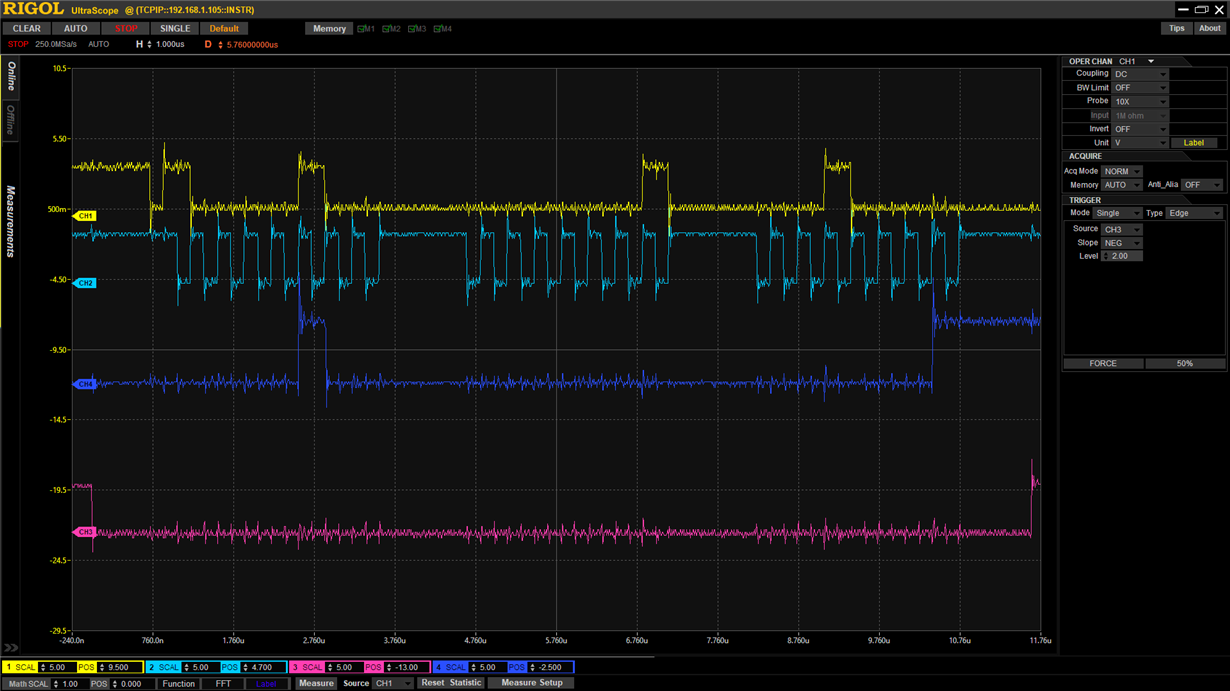

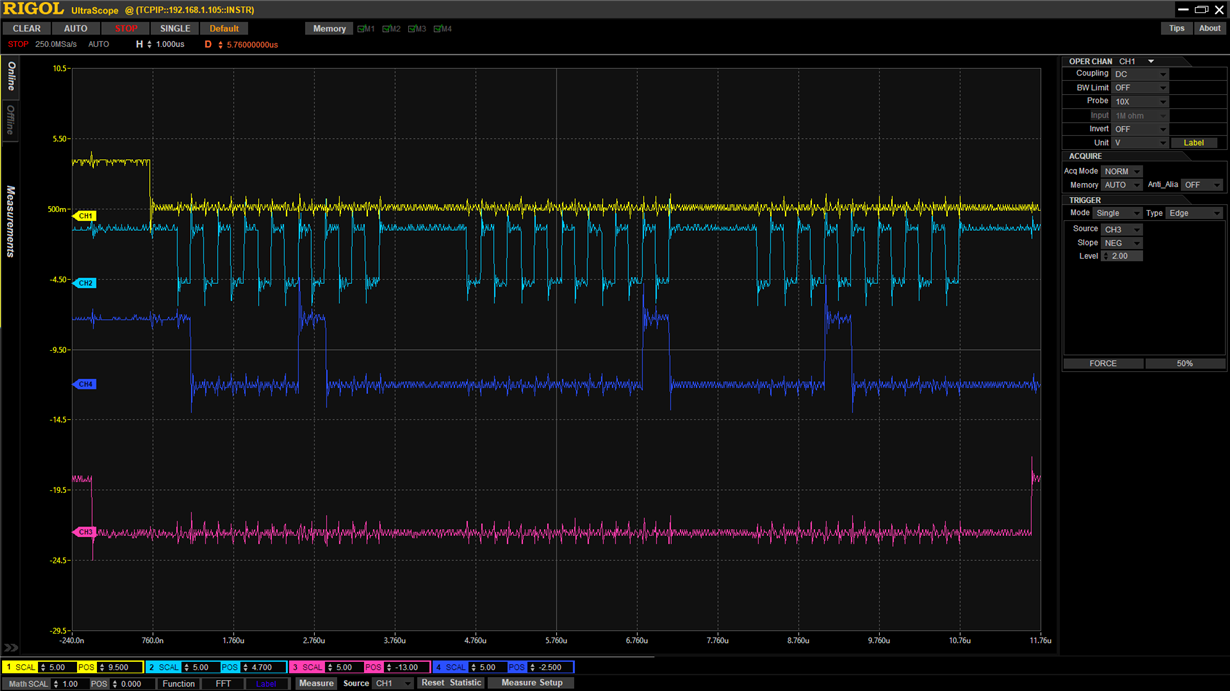

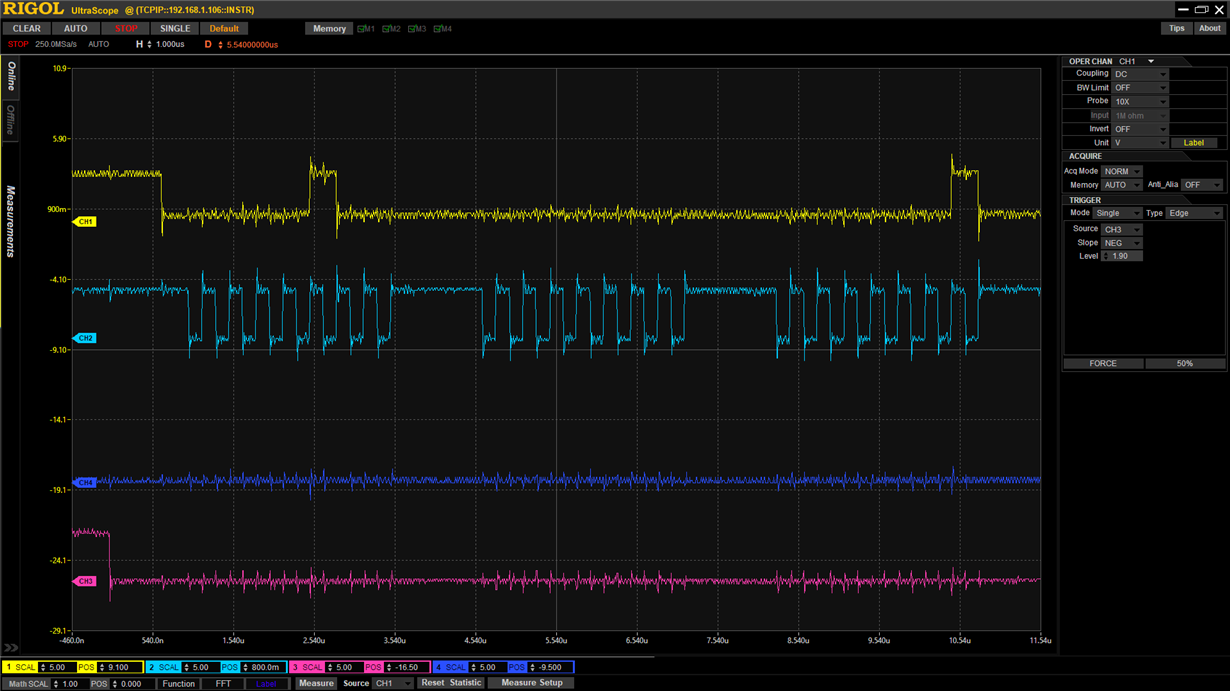

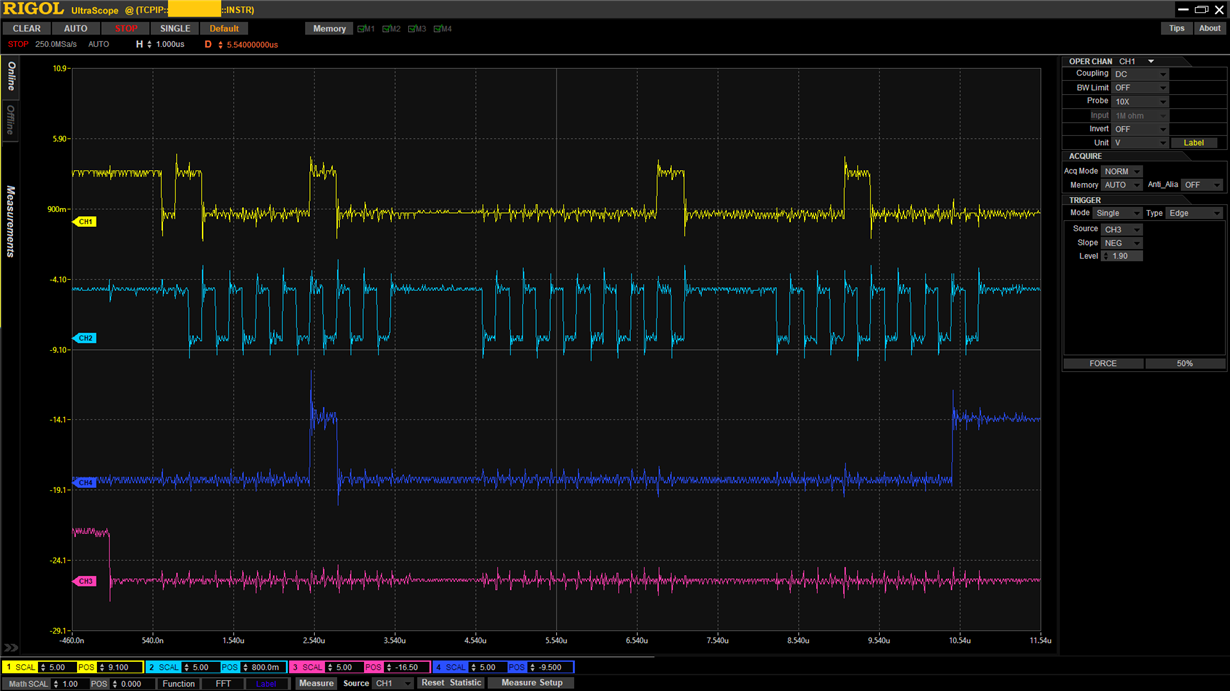

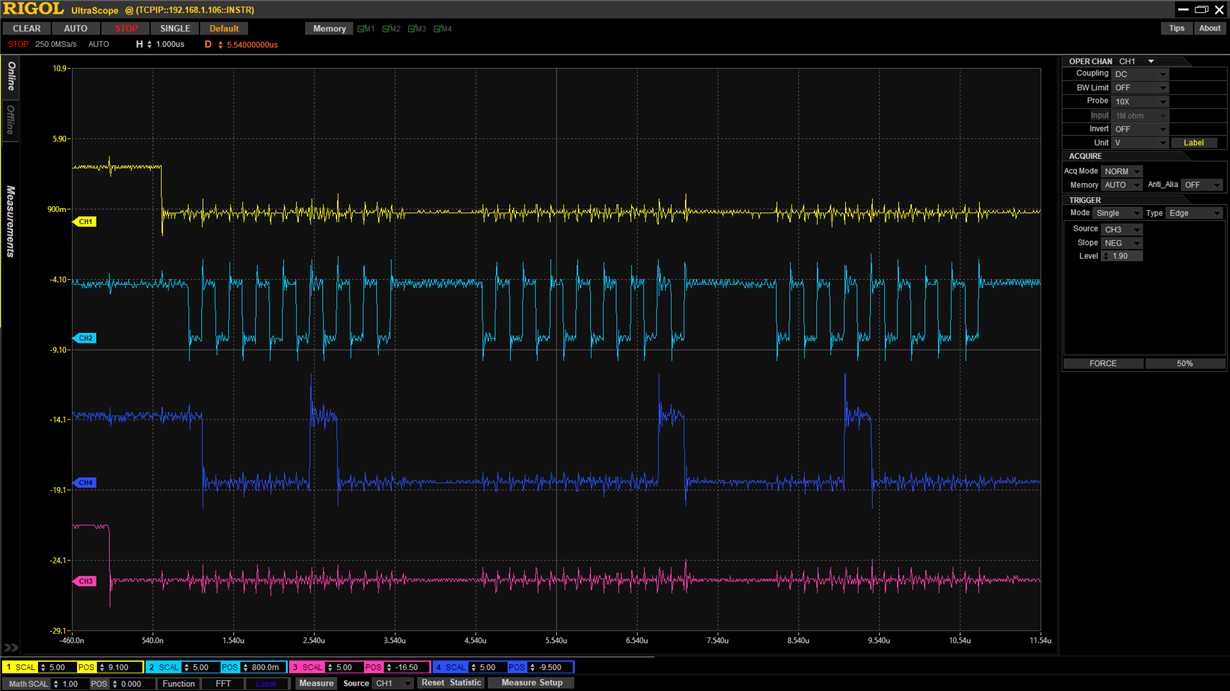

All attempts to read from the device (e.g., status reg=0x0B or POR config reg=0x2) after power reset shows that the device is still in the daisy chain mode. (MISO is echo of last command delayed by 24 bit; and user bit is also 0). I also tried reset the device via register (reg=0x1; data=0x0001) at the startup.

Does the device defaults to daisy chain mode when BBC is not enabled/configured (via 0x06 and 0x07)? or is there some other issues?

[BBC is disabled for now since VPOS and VNEG of the BBC will be used to power a analog switch (has 3.3V SPI) - not wired at the moment].

Note: I have been testing DAC8775 using the EVAL board, and noticed that I had to replace NOP=[0x00,0x00,0x00] with [0xFF,0xFF,0xFF] in the read command; testing with both MSP432 and Python at the test points of the EVAL board and was working. I tried both 0x00 and 0FF with DAC8771 but nothing works.

Thanks for your help.