Hello,

I start looking into the "slac748_adc12dj3200_A10fpga_jesd204b_from_TI", the source code and user guide etc.

I noticed that the JESD204B configuration seems different between user guide and the source files, in which the source file are restored with Quartus Prime Pro version 16.1.

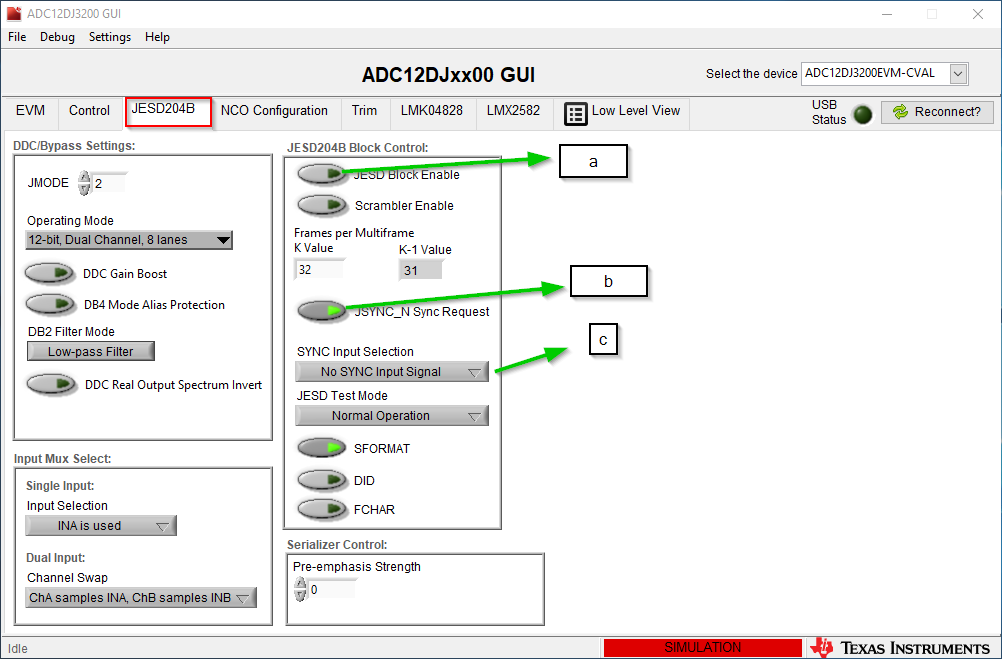

For example, it shows K= 4 in the user guide for configuring ADC but the K = 32 in "altera_jesd2041_.... v", see below. The values below matched with QSYS setting.

altera_jesd2041_altera_jesd204_161_kzbcg4i #(

.DEVICE_FAMILY ("Arria 10"),

.SUBCLASSV (1),

.PCS_CONFIG ("JESD_PCS_CFG2"),

.L (8),

.M (4),

.F (1),

.N (16),

.N_PRIME (16),

.S (1),

.K (32),

.SCR (1),

.CS (0),

.CF (0),

.HD (0),

.ECC_EN (1),

.DLB_TEST (0),

My questions are:

Q#1, should K =32 or K=4 be used? Also other parameters if differed.

Also, in the user guide, it states "In this EVM revision P & N pins of upper four SERDES lanes are swapped, hence Rx lane polarity inversion is implemented in the design to address that." So,

Q#2, which FPGA module or block address it.

Hope to hear from ASAP.