Our KMM customers encounter the following questions during the use of ads5560. Please help to answer them

1、 Whether the clock can adopt the differential clock output by FPGA, or still have to use a special clock chip to form a fully differential clock?

2、 The delay of the output clock controlled by the control pin SEN corresponds to which signal is delayed (input clock, or output data?)?

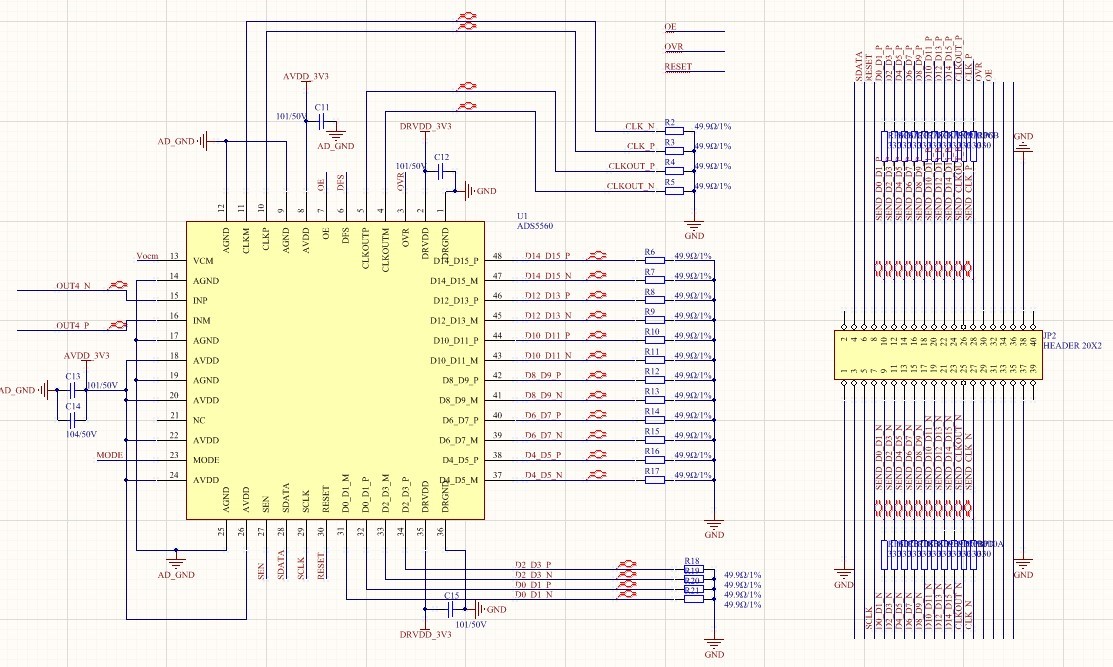

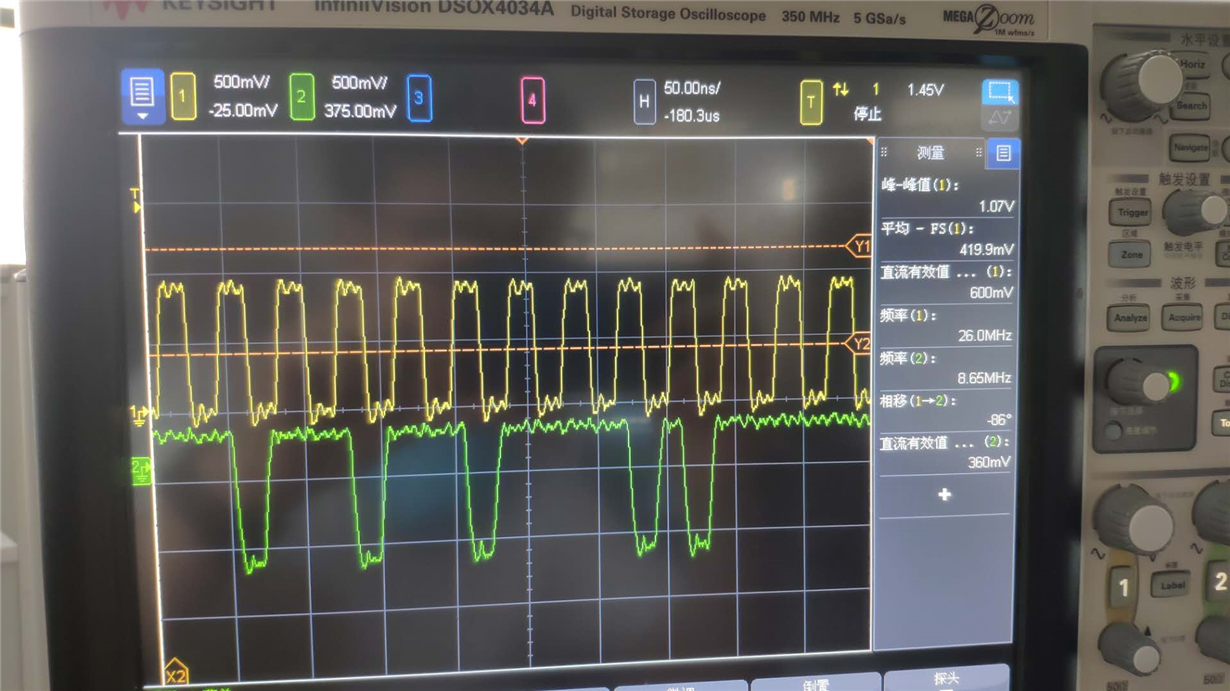

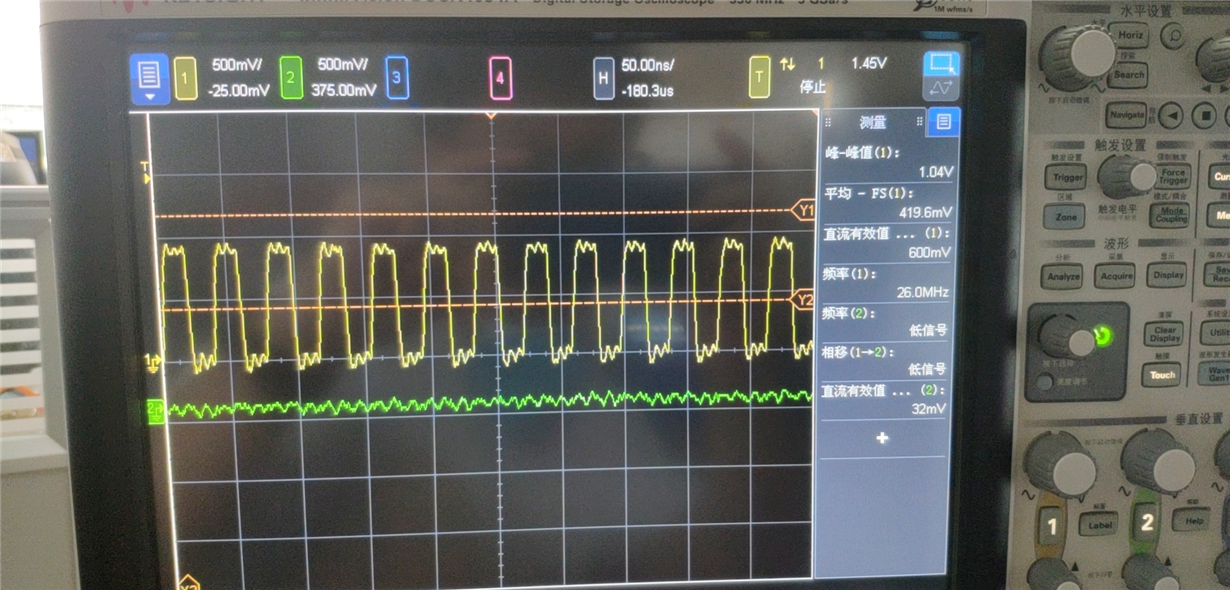

3、 What kind of matching method should be used for impedance matching of data output pins.?The matching method we currently use is to connect a 50Ω resistor between the output pin and GND.The matching circuit of our board is as follows:

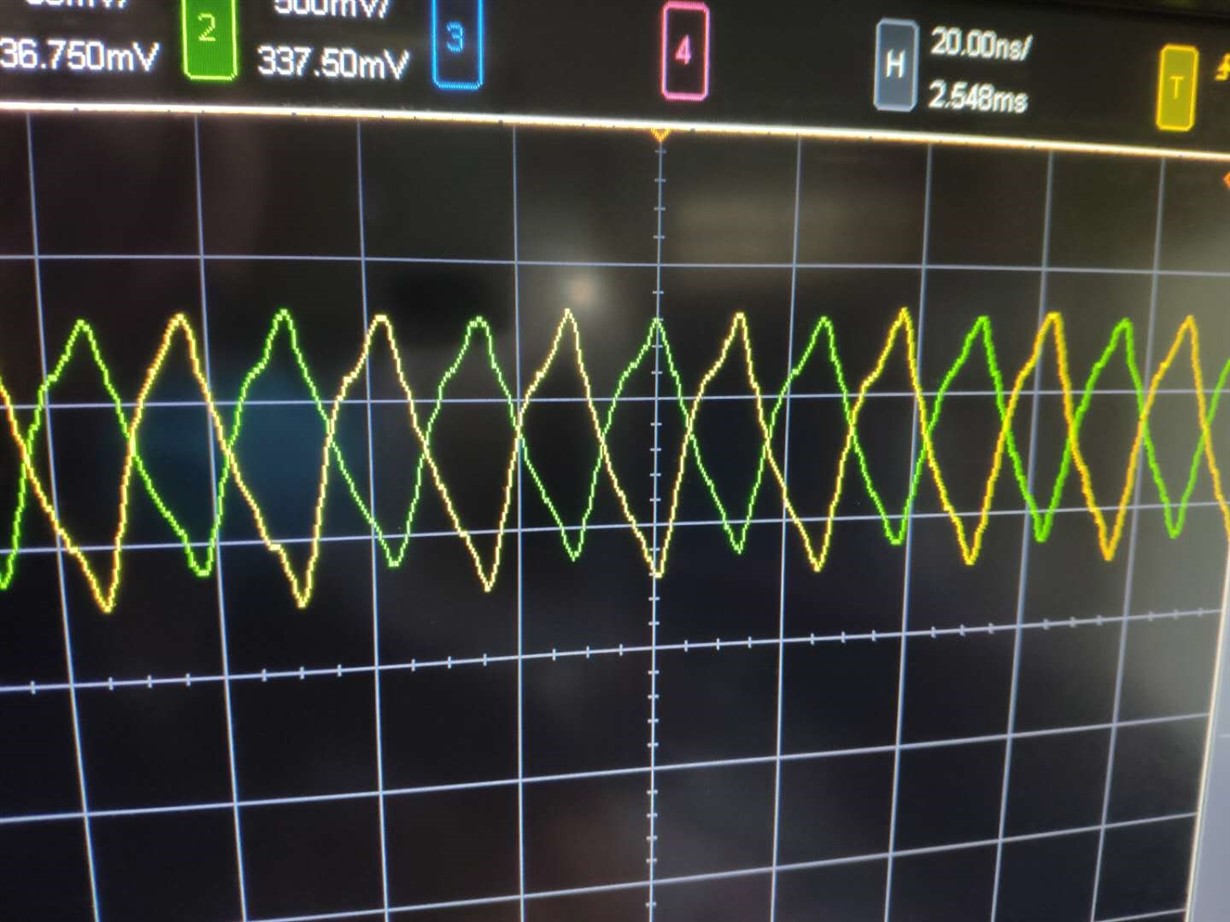

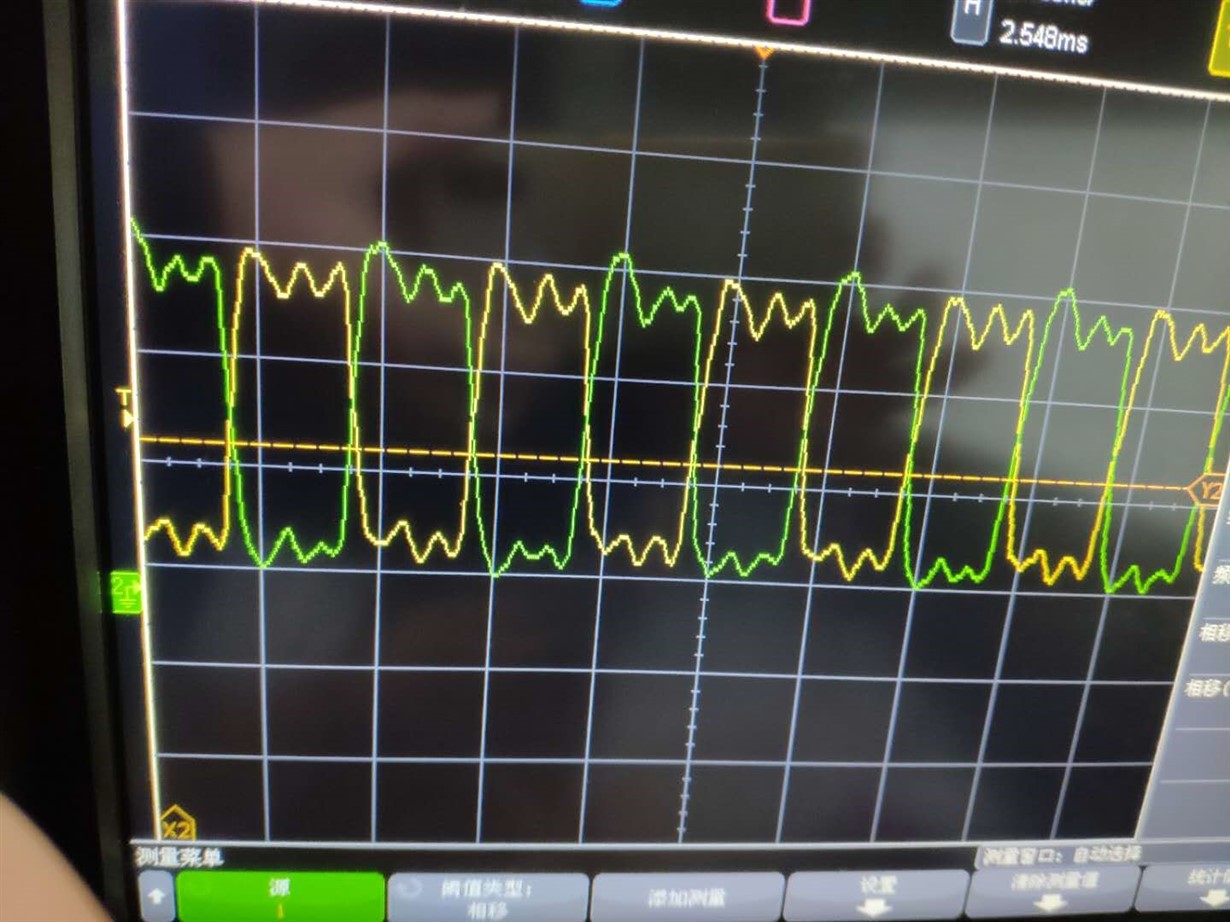

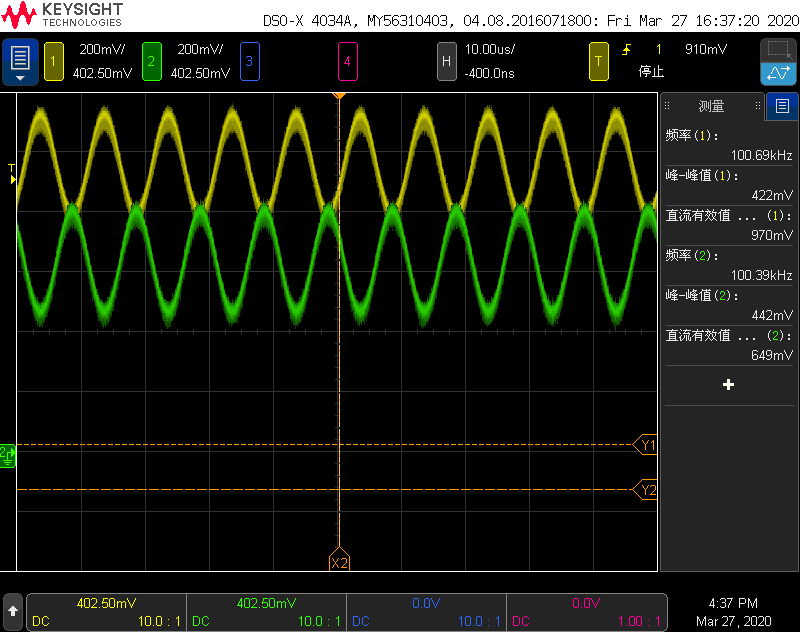

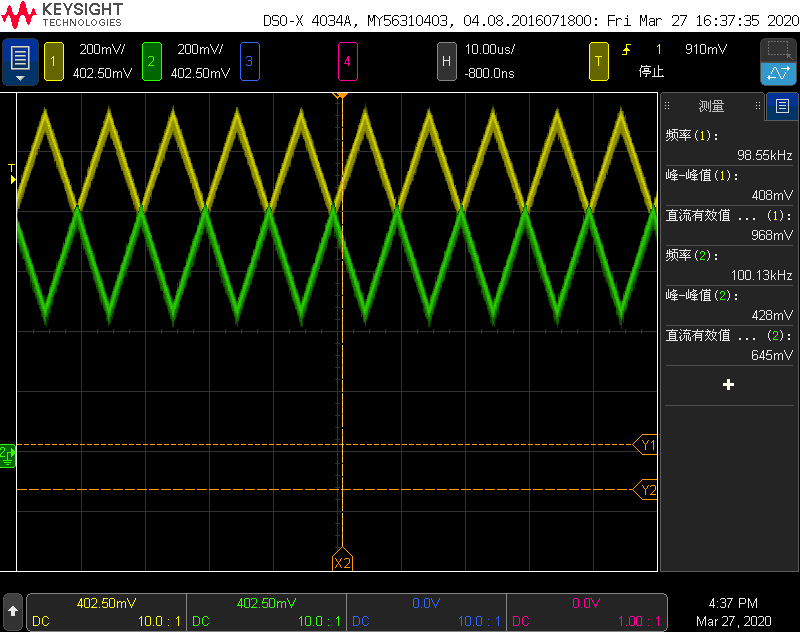

b、Waveform after matching:

4、Could you provide some data processing routines for ADS5560 when use FPGA?

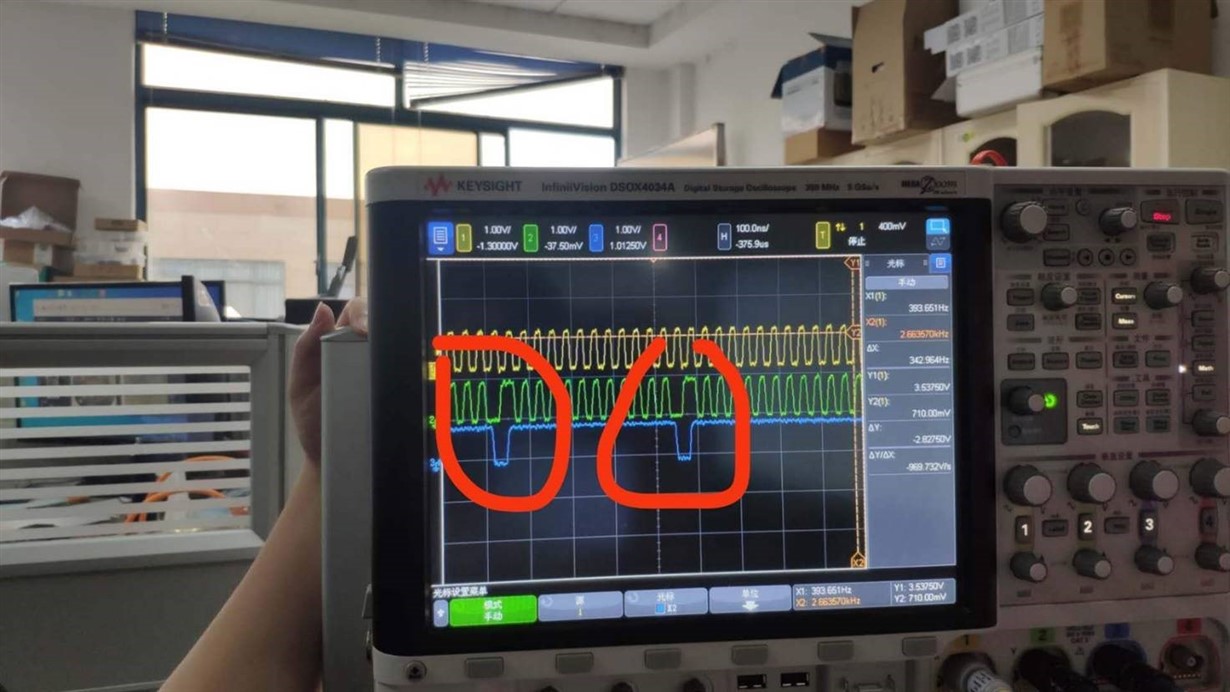

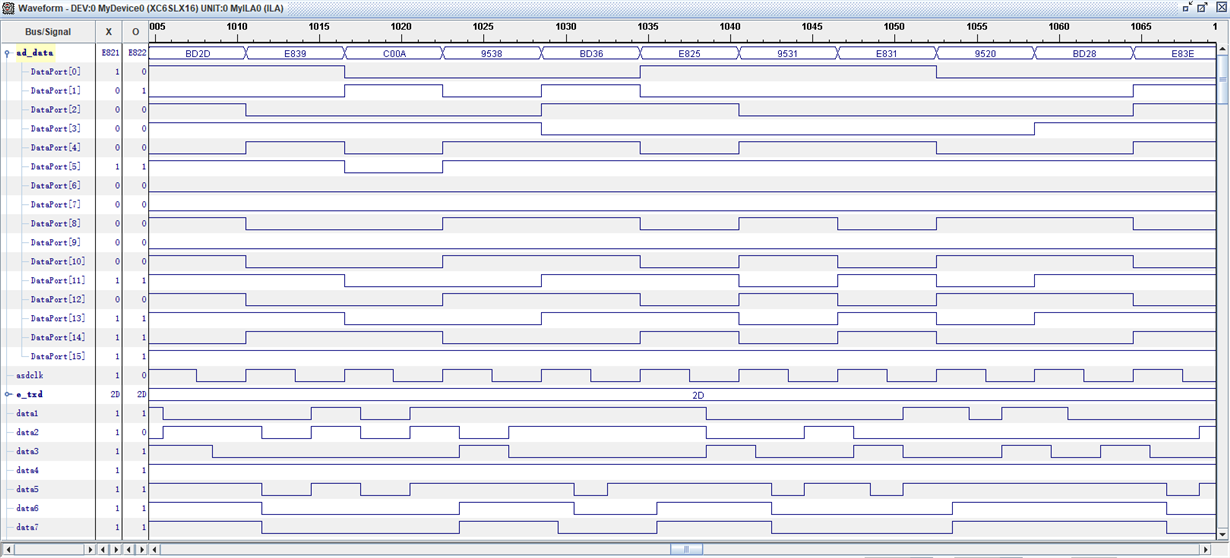

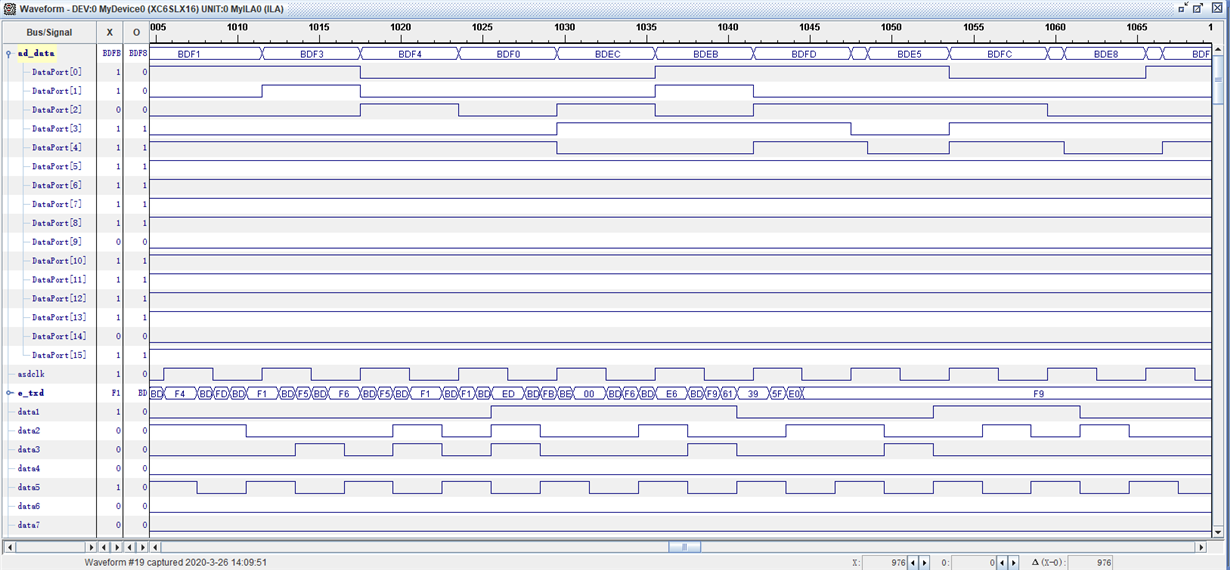

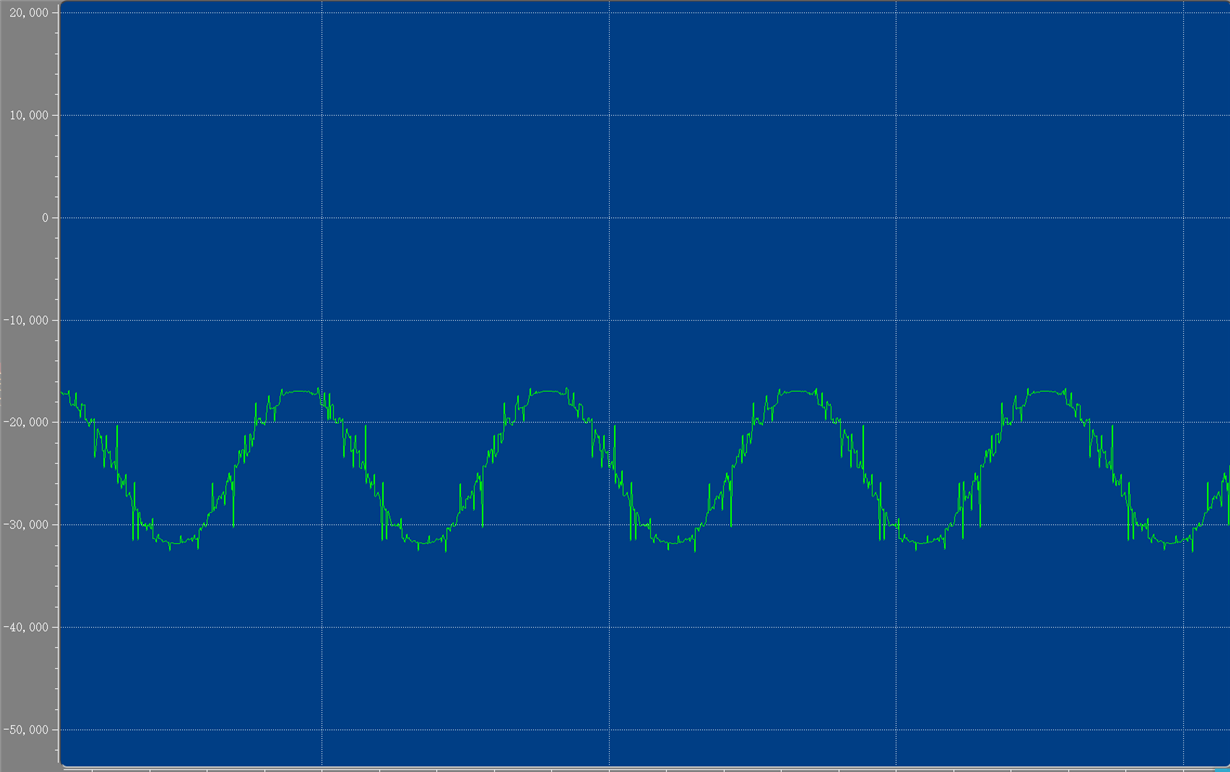

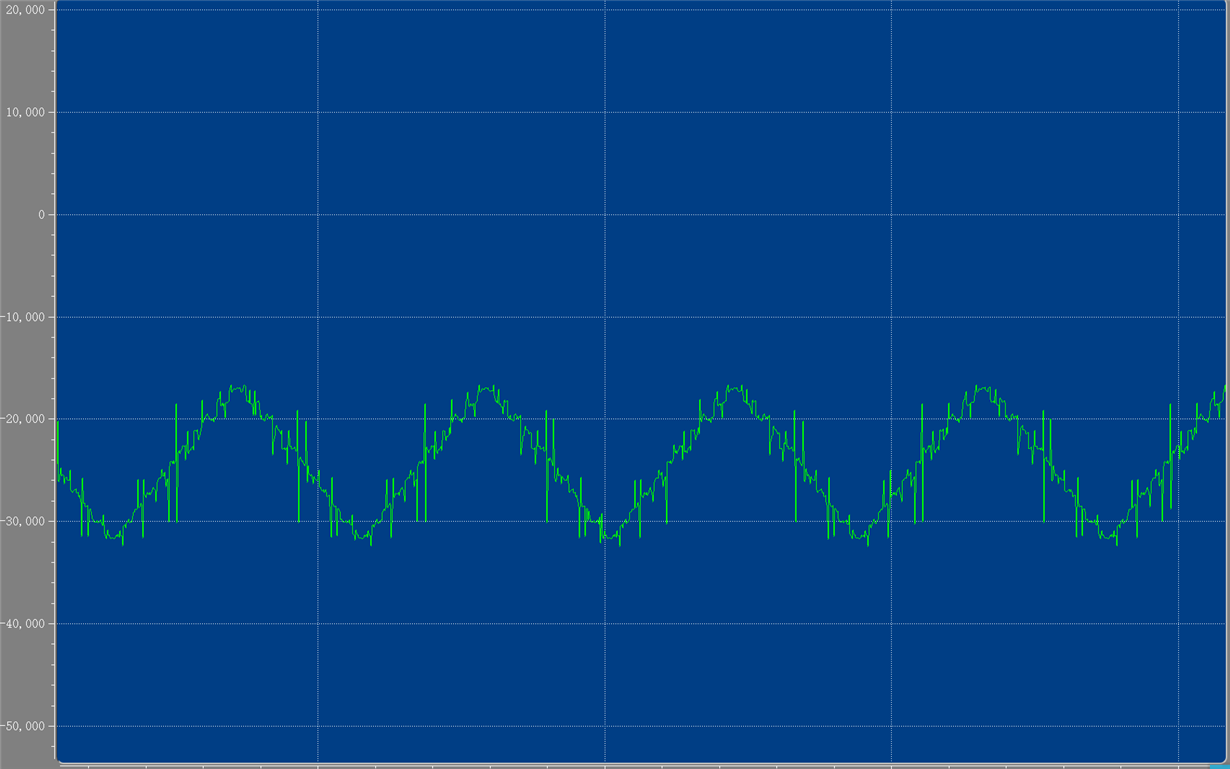

5、In addition, we compare the difference between our board and ads5560evm: our board uses the differential clock output by FPGA, while ads5560evm uses the clock output by special clock chip. We connect the input to GND and sample data14 and data15 (pin47 and pin48) all the time. Occasionally, we can catch a signal of 1, as shown in the figure below, which leads to the spike of sampling data. I don't know if it's because of the clock signal?