Hello TI support,

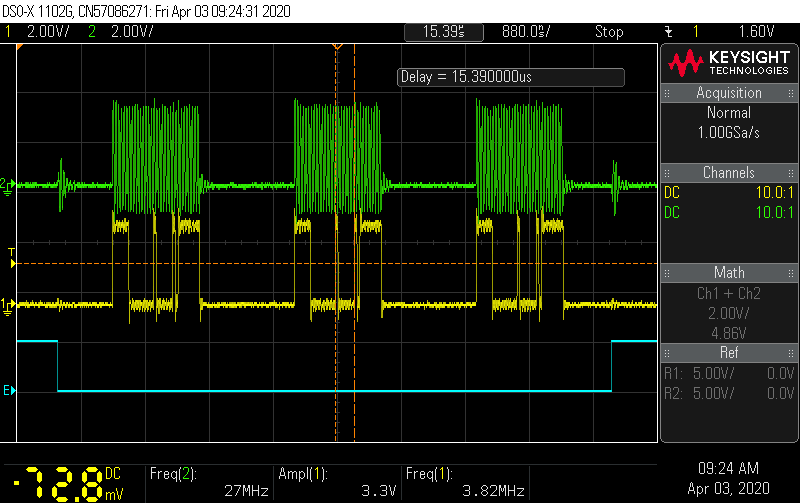

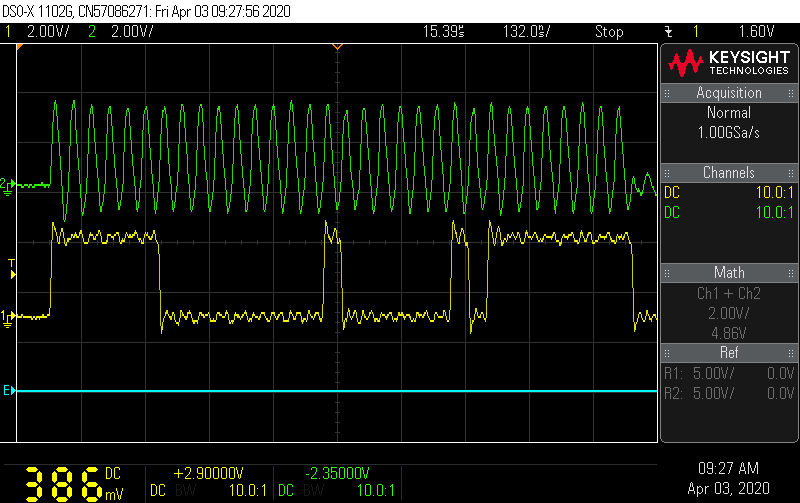

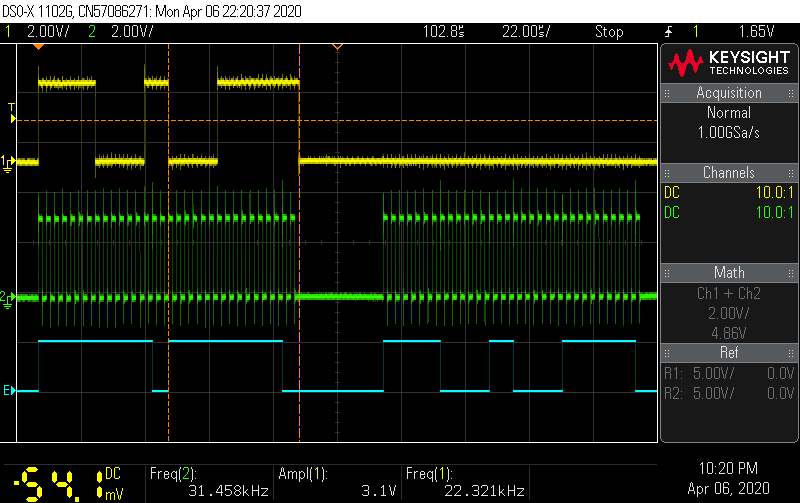

im trying to build up an analog frontend with the ADS8556 chip. The circuit is shown in the appended PDF. The ADS is used in software mode to configure the internal registers and control the reference DAC output voltage. The ADC is controlled via an ESP32 using its SPI. I'm writing the 32 Bit number 11111110 00000001 00000010 11111111 to it with every readout of the measured values. I controlled the SDI line of the ADC via an oscillosciope and the correct bitpattern is send. But the ADC's REFIO pin still remains exactly 2.5V, no matt what DAC pattern I put in. Even changing bit C18 (VREF) to 1, which should result in 3V reference voltage, doesn't change anything.

I would be really happy if there are any ideas why it isn't working.

Tanks!