Hi Team,

I have two questions.

----------

[Q1]

We use two differential signals (AIN0 & AIN1 pair, AIN2 & AIN3 pair).

Then, we would like to know the following settling time.

My guess Sequence

1.AIN0 & AIN1 pair are ON and AIN2 & AIN3 pair are OFF

2.To change the differential signals

3.AIN0 & AIN1 pair are OFF and AIN2 & AIN3 pair are ON

4.To occur the settling time ??us (we must wait more than ??us)

5.AIN2 & AIN3 pair data are available for AD conversion

----------

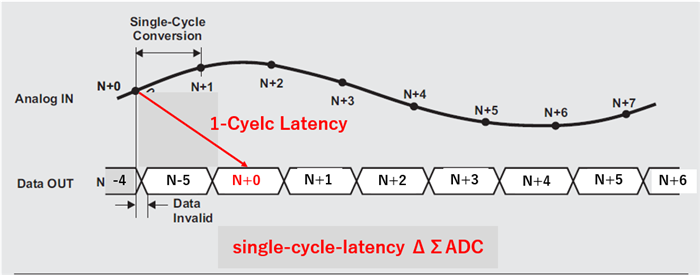

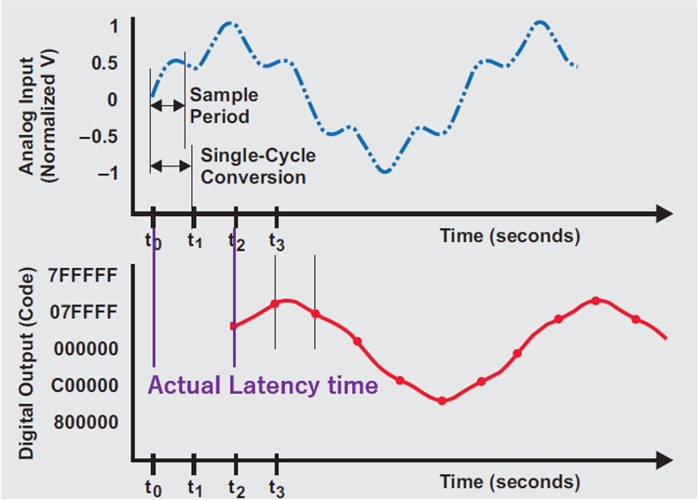

[Q2]

We would like to know the latency(Wait time of from Input analog date to Output digital data).

Could you please let us know if you have any information?

----------

Regards,

Hide