Other Parts Discussed in Thread: ADS7828, ADC128D818

Hi Team,

Customer used ADS7830 to monitor the voltage and find the error this lightly large. Could check if the data is right or have a way to optimize?

----------------------------

We verified ADS7830 function on two units - compare the actual voltage measured at ADS7830 pin and the voltage reported by ADS7830.

Test results on some channels exceed ADS7830 accuracy spec. See attached file for details.

Column B - Actual voltage measured at ADS7830 pin

Column D - Voltage reported by ADS7830

Column E - Difference between two voltages above

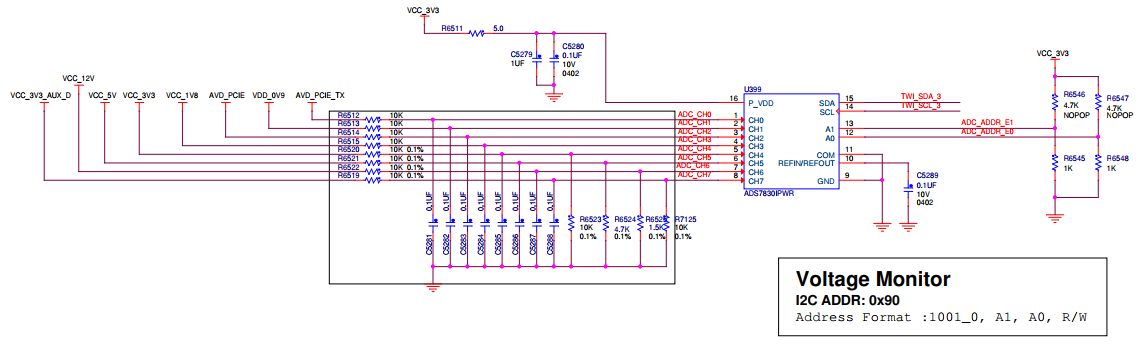

Our design is as below.

Could you help to check and advise the reason for the failures?

| Sample1 | Default Voltage | ||||||

| Channel | Actual voltage measured at ADS7830 pin | ADS7830 register | ADS7830 Report Voltage | Voltage Gap | Max "-" Spec (-0.71 LSB) |

Max "+" Spec (1.22 LSB) |

Result |

| 0 | 0.921 | 5e | 0.91796875 | -0.00303125 | -0.006933594 | 0.011914063 | PASS |

| 1 | 0.919 | 5e | 0.91796875 | -0.00103125 | -0.006933594 | 0.011914063 | PASS |

| 2 | 0.925 | 5e | 0.91796875 | -0.00703125 | -0.006933594 | 0.011914063 | FAIL |

| 3 | 1.811 | b9 | 1.806640625 | -0.004359375 | -0.006933594 | 0.011914063 | PASS |

| 4 | 1.678 | ab | 1.669921875 | -0.008078125 | -0.006933594 | 0.011914063 | FAIL |

| 5 | 1.622 | a6 | 1.62109375 | -0.00090625 | -0.006933594 | 0.011914063 | PASS |

| 6 | 1.568 | a0 | 1.5625 | -0.0055 | -0.006933594 | 0.011914063 | PASS |

| 7 | 1.721 | b0 | 1.71875 | -0.00225 | -0.006933594 | 0.011914063 | PASS |

| Sample1 | High Voltage | ||||||

| Channel | Actual voltage measured at ADS7830 pin | ADS7830 register | ADS7830 Report Voltage | Voltage Gap | Max "-" Spec (-0.71 LSB) |

Max "+" Spec (1.22 LSB) |

Result |

| 0 | 0.942 | 60 | 0.9375 | -0.0045 | -0.006933594 | 0.011914063 | PASS |

| 1 | 0.938 | 60 | 0.9375 | -0.0005 | -0.006933594 | 0.011914063 | PASS |

| 2 | 0.934 | 5f | 0.927734375 | -0.006265625 | -0.006933594 | 0.011914063 | PASS |

| 3 | 1.902 | c2 | 1.89453125 | -0.00746875 | -0.006933594 | 0.011914063 | FAIL |

| Sample1 | Low Voltage | ||||||

| Channel | Actual voltage measured at ADS7830 pin | ADS7830 register | ADS7830 Report Voltage | Voltage Gap | Max "-" Spec (-0.71 LSB) |

Max "+" Spec (1.22 LSB) |

Result |

| 0 | 0.906 | 5c | 0.8984375 | -0.0075625 | -0.006933594 | 0.011914063 | FAIL |

| 1 | 0.896 | 5b | 0.888671875 | -0.007328125 | -0.006933594 | 0.011914063 | FAIL |

| 2 | 0.9 | 5c | 0.8984375 | -0.0015625 | -0.006933594 | 0.011914063 | PASS |

| 3 | 1.723 | b0 | 1.71875 | -0.00425 | -0.006933594 | 0.011914063 | PASS |

| Sample1 | Default Voltage | ||||||

| Channel | Actual voltage measured at ADS7830 pin | ADS7830 register | ADS7830 Report Voltage | Voltage Gap | Max "-" Spec (-0.71 LSB) |

Max "+" Spec (1.22 LSB) |

Result |

| 0 | 0.922 | 5e | 0.91796875 | -0.00403125 | -0.006933594 | 0.011914063 | PASS |

| 1 | 0.921 | 5e | 0.91796875 | -0.00303125 | -0.006933594 | 0.011914063 | PASS |

| 2 | 0.923 | 5e | 0.91796875 | -0.00503125 | -0.006933594 | 0.011914063 | PASS |

| 3 | 1.806 | b8 | 1.796875 | -0.009125 | -0.006933594 | 0.011914063 | FAIL |

| 4 | 1.675 | ab | 1.669921875 | -0.005078125 | -0.006933594 | 0.011914063 | PASS |

| 5 | 1.621 | a5 | 1.611328125 | -0.009671875 | -0.006933594 | 0.011914063 | FAIL |

| 6 | 1.568 | a0 | 1.5625 | -0.0055 | -0.006933594 | 0.011914063 | PASS |

| 7 | 1.718 | af | 1.708984375 | -0.009015625 | -0.006933594 | 0.011914063 | FAIL |

| Sample1 | High Voltage | ||||||

| Channel | Actual voltage measured at ADS7830 pin | ADS7830 register | ADS7830 Report Voltage | Voltage Gap | Max "-" Spec (-0.71 LSB) |

Max "+" Spec (1.22 LSB) |

Result |

| 0 | 0.943 | 60 | 0.9375 | -0.0055 | -0.006933594 | 0.011914063 | PASS |

| 1 | 0.94 | 60 | 0.9375 | -0.0025 | -0.006933594 | 0.011914063 | PASS |

| 2 | 0.932 | 5f | 0.927734375 | -0.004265625 | -0.006933594 | 0.011914063 | PASS |

| 3 | 1.896 | c2 | 1.89453125 | -0.00146875 | -0.006933594 | 0.011914063 | PASS |

| Sample1 | Low Voltage | ||||||

| Channel | Actual voltage measured at ADS7830 pin | ADS7830 register | ADS7830 Report Voltage | Voltage Gap | Max "-" Spec (-0.71 LSB) |

Max "+" Spec (1.22 LSB) |

Result |

| 0 | 0.906 | 5c | 0.8984375 | -0.0075625 | -0.006933594 | 0.011914063 | FAIL |

| 1 | 0.898 | 5c | 0.8984375 | 0.0004375 | -0.006933594 | 0.011914063 | PASS |

| 2 | 0.899 | 5c | 0.8984375 | -0.0005625 | -0.006933594 | 0.011914063 | PASS |

| 3 | 1.718 | af | 1.708984375 | -0.009015625 | -0.006933594 | 0.011914063 | FAIL |

Thanks.