Other Parts Discussed in Thread: TIDA-00810, CDCLVC1102

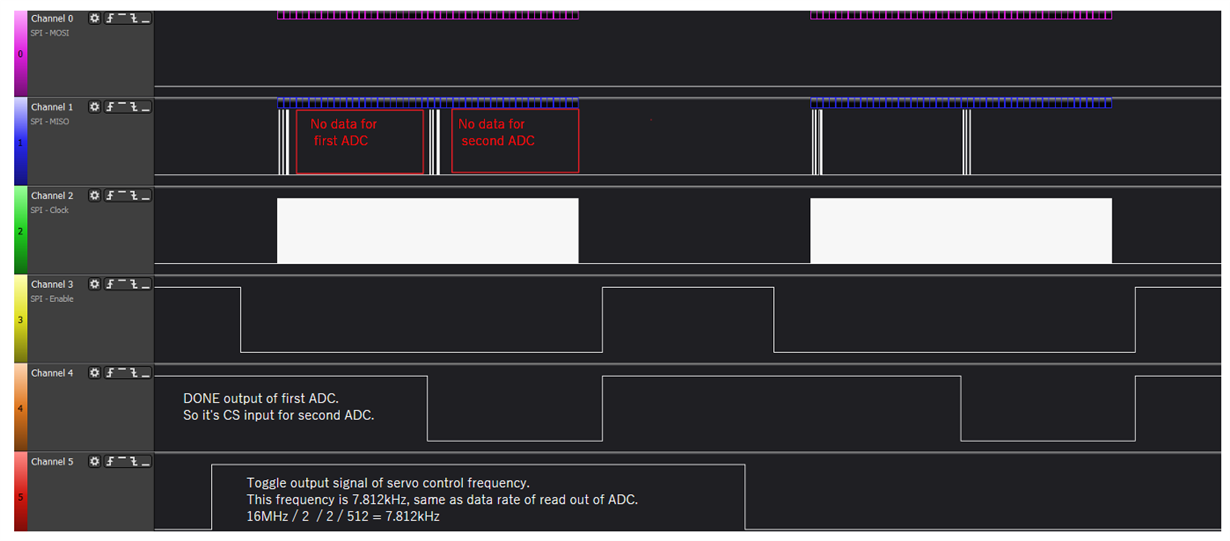

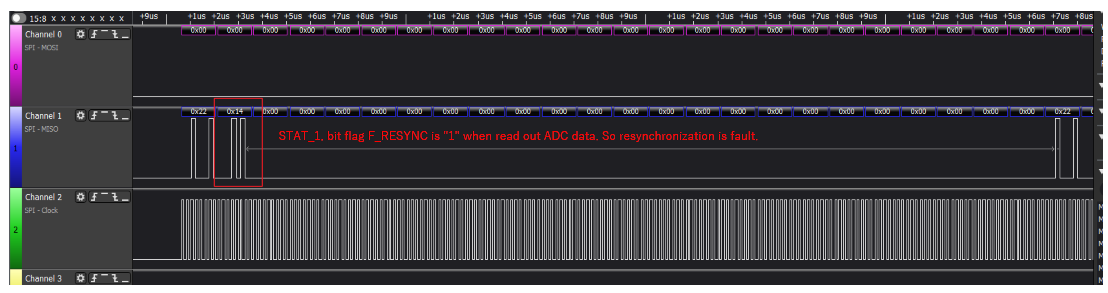

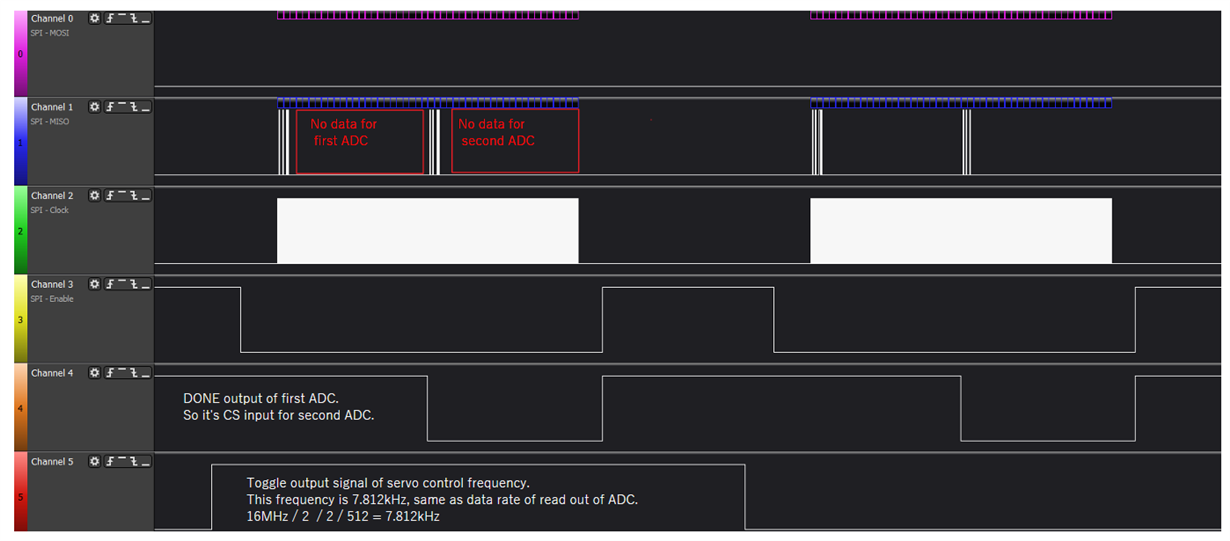

AD conversion value is not returned at multiple device configuration using synchronous slave mode.

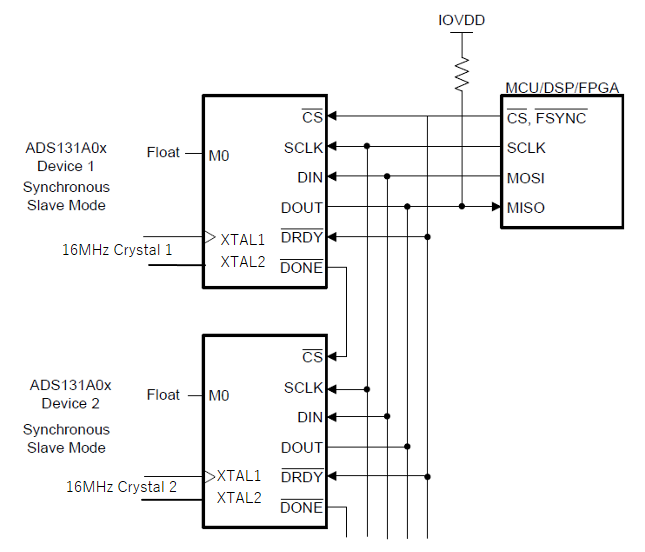

I conect two ADCs and mode settings are 32bit, no hamming, slave mode. Also i use 16MHz crystal and set data rate at 16MHz/2/2/512=7812Hz. So i ask AD values every 7812Hz period, but i can't get AD value. AD values are zeros.

How can i get AD values?