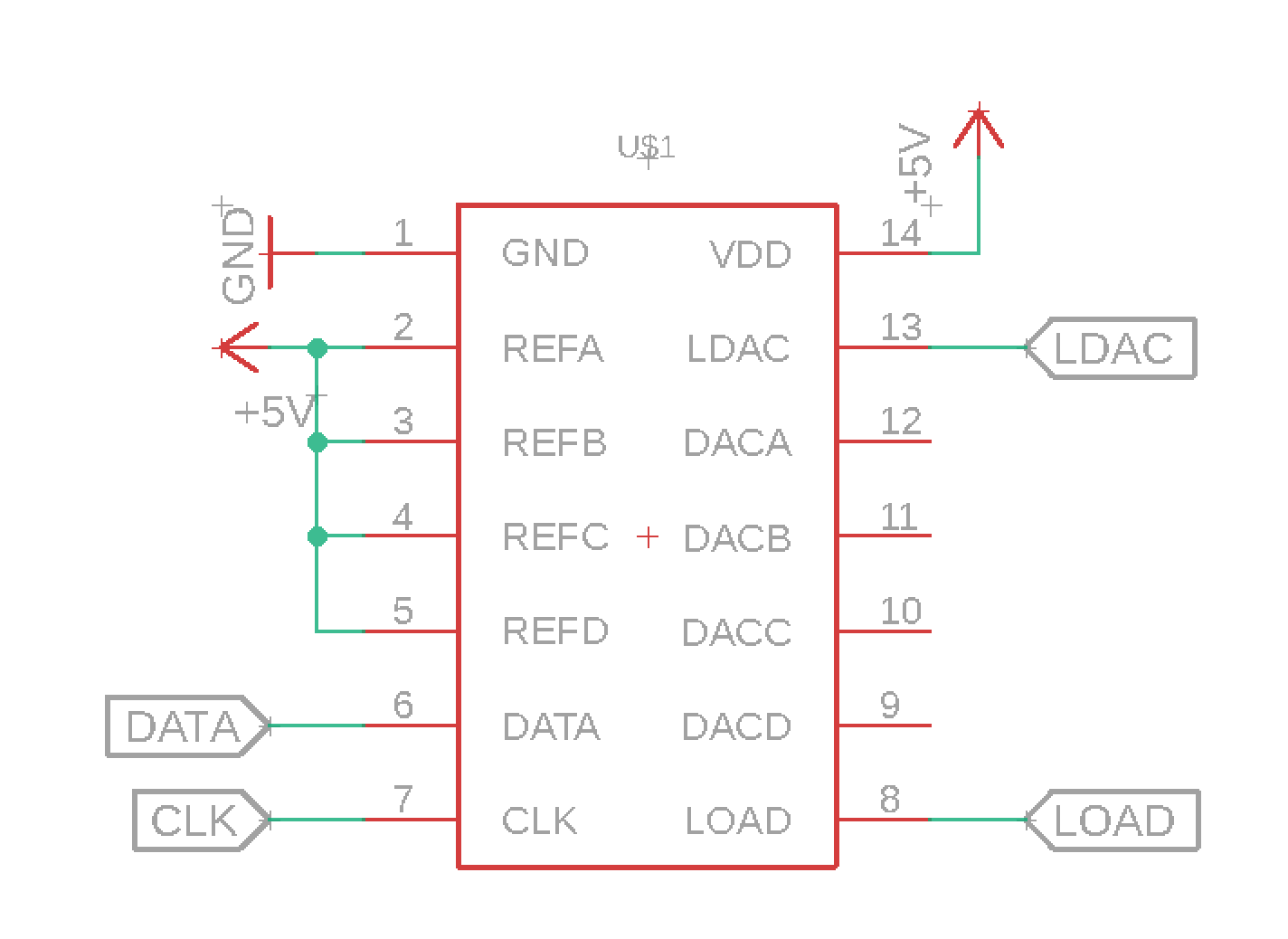

I am attempting to use the TLC5620, but I am unable to generate the desired output. I am using the following configuration:

Vdd = REFA-D = 5 V

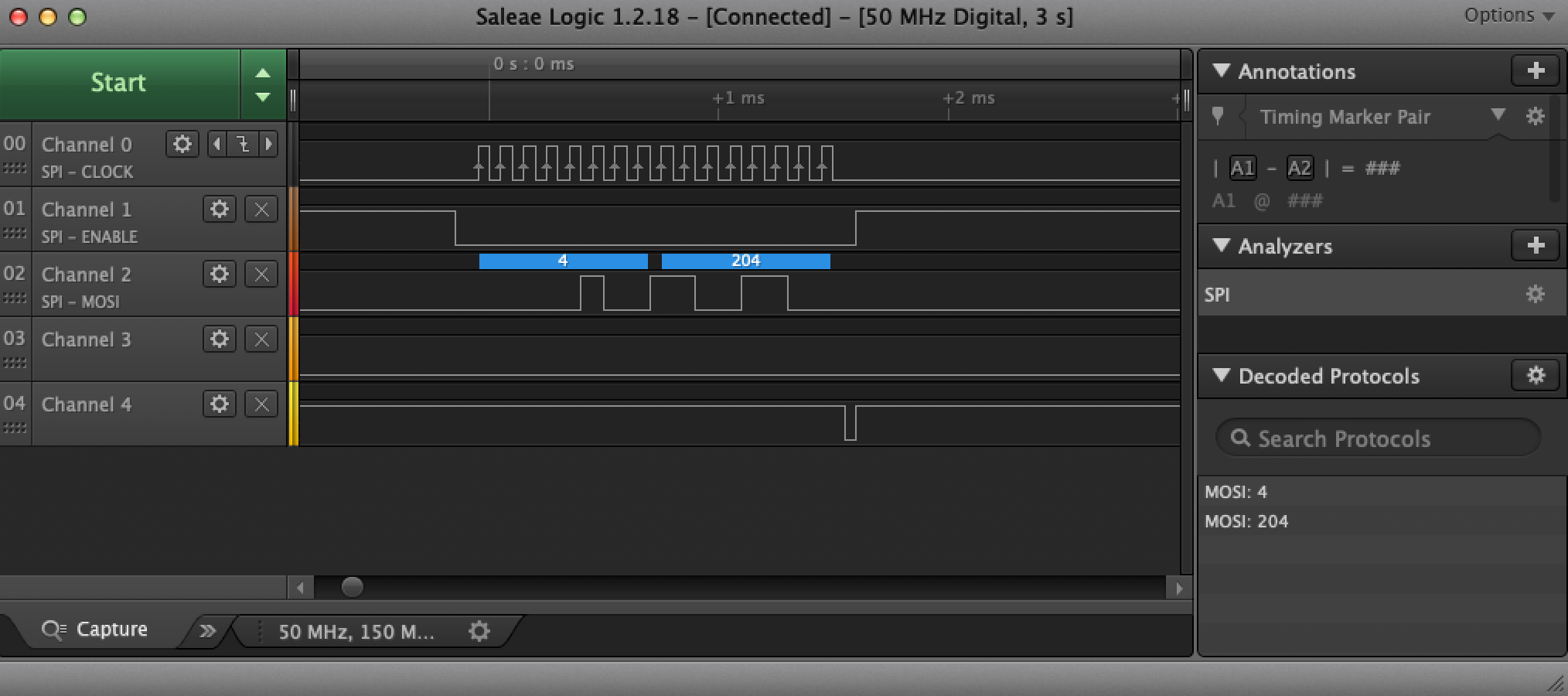

As an example: I tried to generate a 4 V output on DACB. The SSI signal (shown below) is as expected. The connections in the figure are:

- Channel 0 [Clock] -> CLK (Pin 7)

- Channel 1 [Enable] -> LDAC (Pin 13)

- Channel 2 [MOSI] -> DATA (Pin 6)

- Channel 3 -> unused

- Channel 4 -> LOAD (Pin 8). Channel 3 is unused.

The first byte sets the Address as DACB with RNG = 0, and the data byte should set the output at 4 V (5 * 204/256 = 3.984 V. However, the output this generates is 2.059 V on DACA.

What am I doing incorrectly?