Now we want to use PCM1865 combined with DM8168.

But I have some questions:

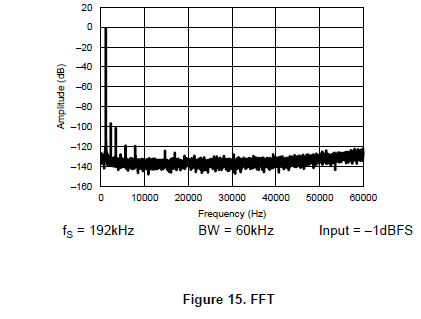

1.In datasheet,9.1.4 Main Audio ADCs..it says that 40KHZ adc.

And in Page2 Typ.Performance it says that sampling frequency: 32KHZ to 192KHZ

40KHZ audio,and 192K sr?I think sr=2*bandwidth.

Is there something wrong?

2.Auto clock configure.

If we are use PCM1865 in master mode,can pcm1865's clock be auto configured?

I am a liitle puzzled,as it says that The dividers are auto configured based on clock rate detection in 9.13.3 of datasheet.How to detect clock rate?

3.Can I set PCM1865's sample frequency in 22.05K?

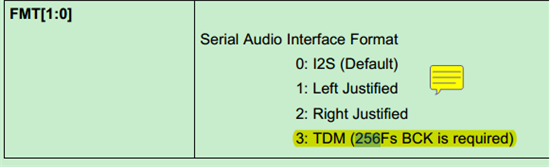

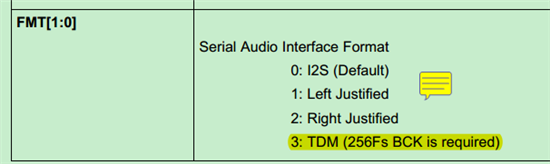

In Page/Register 15

there is not a case that sample frequency is 22.05K.Why?Can I set pcm1865's sample frequency to 22.05K?

BR!