Hi,

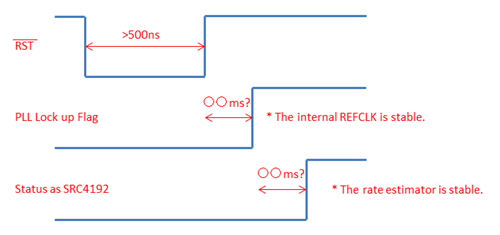

Could you please tell us the pll lock-up time and the necessary time to be stable as the sample rate converter for SRC4192?

When does the pll lock up in the reference clock block if RCKI is input to SRC4192 and RST is assert low to high?

Moreover, when does the rate estimator block stably work as the sample rate converter if the internal REFCLK is stable and SDIN is input to SRC4192?

Best Regards,

Kato