Summary:

Using 3 AIC3254 devices in TDM mode sharing a single 8Khz mono audio bus from/to an FPGA.

1/ What is the best strategy in choosing the clock scheme. (master / slave)

2/ What is WCLK frequency in TDM mode given every L/R channel will be used a sa single mono. (Supposed to be 3xfs).

3/ In this particular case (FPGA) wouldn't it be more practical / efficient to split the audio buses in 3 fully independant audios to/from the FPGA and drive

each of the audio clocks separetely.

Your answer to the 1st point:

See this app note: http://www.ti.com/lit/pdf/slaa469

BCLK output from FPGA should have low jitter: 100ps cycle to cycle rms or less.

If not possible to generate such a clean BCLK, you could have one of the AIC3254 take in MCLK and generate BCLK for the other 2 devices and also make FPGA I2S slave. However, 64MHz is too fast for MCLK input pin of AIC3254, so you would need to divide by 2.

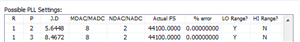

Below is an example for PLL settings if using 32MHz as MCLK input.

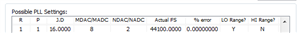

For the other 2 AIC3254s, you can use BCLK as MCLK source. In such case, if BCLK = 128*FS = 5644.8 MHz, then you can use the settings below: