Hi,

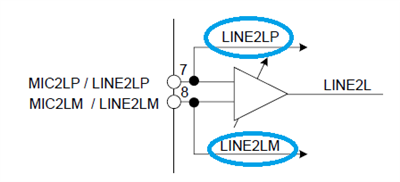

I am working with TLV320AIC3106 codec IC. I have FM/AM radio connect to LINE2(L/R)+ and want it output to (LEFT/RIGHT)_LO+. How should I configure related register to switch to LINE2 through I2C?

My current setting:

Register 37 -> 0x00 (turn off DAC)

Register 80 -> 0x80 (route LINE2L to LEFT_LOP/M)

Register 90 -> 0x80 (route LINE2R to RIGHT_LOP/M)

Register 108 - > 0x44 (configure analog signal bypass switch)

According the settings above, I only got some noise.

Are there any other configurations I should set?

Thanks,

Josh