Hi there,

I'm still working with the TLV320AIC3254 on a similar project,but I gave up the inverted inputs issue (original topic).

Indeed, I decided to use a single better microphone on only one input, avoiding the sum/difference issue. However, to have a quick overview, I first didn't modify the PF (you can read the config on the original topic) just to check if the new micro+amplifier were correct. They work ! But during these quick tests, I noticed a weird behaviour of my inputs and I would like to get your opinion/solution about it.

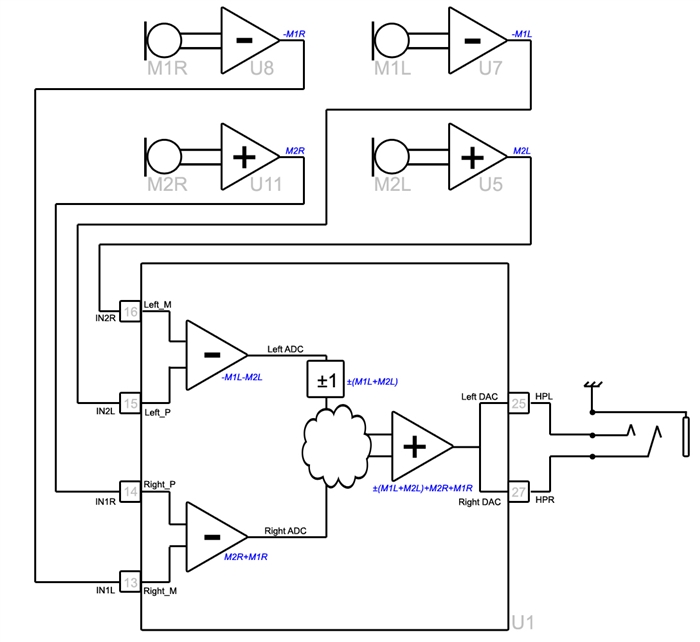

I plugged my preamp on IN1R and grounded the 3 other inputs. As the original program summed them all together (summed the 2 differential pairs, which were in fact the difference of 2 opposite signals each... anyway), I was supposed to get IN1R+IN1L+IN2R+IN2L on my output (HPR/L), and as inputs were all grounded except IN1R, I just was supposed to get IN1R+0+0+0. Right ?

Definitly not ! I got a weird silent output which cracks (like over clipping) when the sound becomes too loud or when blowing on the mic. I first thought about grounding issue or instability... But as this mic signal is used elsewhere on the board, I knew the signal was good and the ground didn't have such a huge weakness... And I finally found that when the 3 others input pins where let unplugged, my ouput was good as IN1R. Why !?

Why do you think grounding inputs can involve such a weird behaviour whereas letting them unplugged gives me the normal signal ?

Cheers !