I am trying to run a simple digital loopback in a 3254 codec using DSP_D_DSP_A component in a real design using PPS.

The i2s is multiplexed over 3x3254 devices using i2s mode.

I have already discarded bad 3254 clk configuration as this configuration (clks) works fine in some other tests.

Device0 provides clocks setup for device1 and 2.

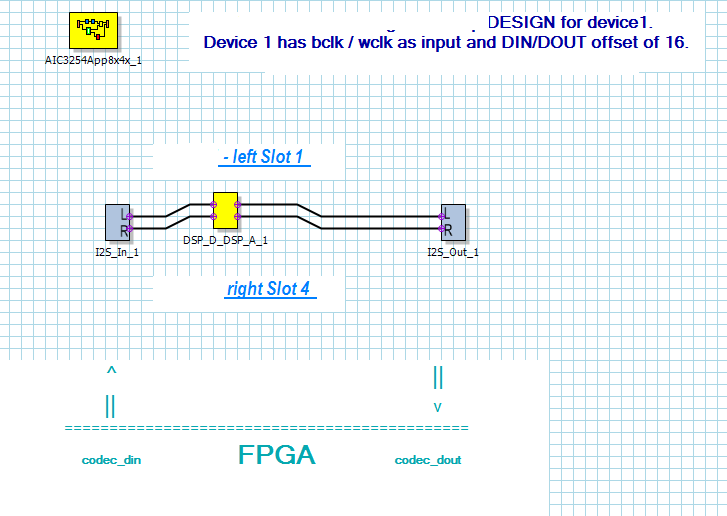

PPS design below: nothing magic very simple design:

When I observ with a scope the DIN my design it works exactly as expected (din enters slot1 very cleanly). At dout I have a definitive flat line.

I was expecting the input to be replicated to dout. What's wrong here ? I have tried synchronous mode with no help.

I have been reading this forum thread "PurePath digital-digital model for digital interface loopback" but this does not help me.

Any idea where the prblem could be ?

Thanks for the help.