Hi

The DIX9211 looks very flexible. Especially the multichannel routing function and the input / output sampling frequency calculators are very interesting.

I have a question based on my experience with Wolfson's WM8805 s/pdif receiver which i have used so far. It indicates (of course in software operation mode) only four recovered frequencies: 32KHz, 44.1 or 48KHz, 88.2 or 92KHz and 192KHz. That is a very rough indication and the 176.4KHz is not included. Also, its Input Channel Status registers are out of order. For that reason i decided to replace it.

DIX9211 can realy indicate all sampling frequencies as is stated in the manual through the relevant i/o calculators?

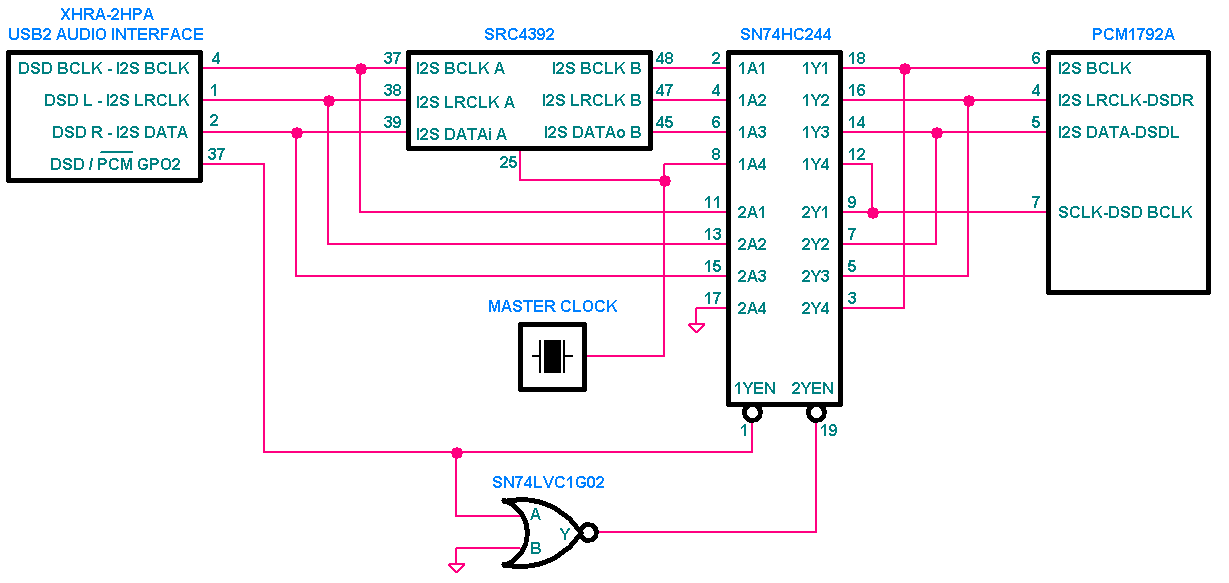

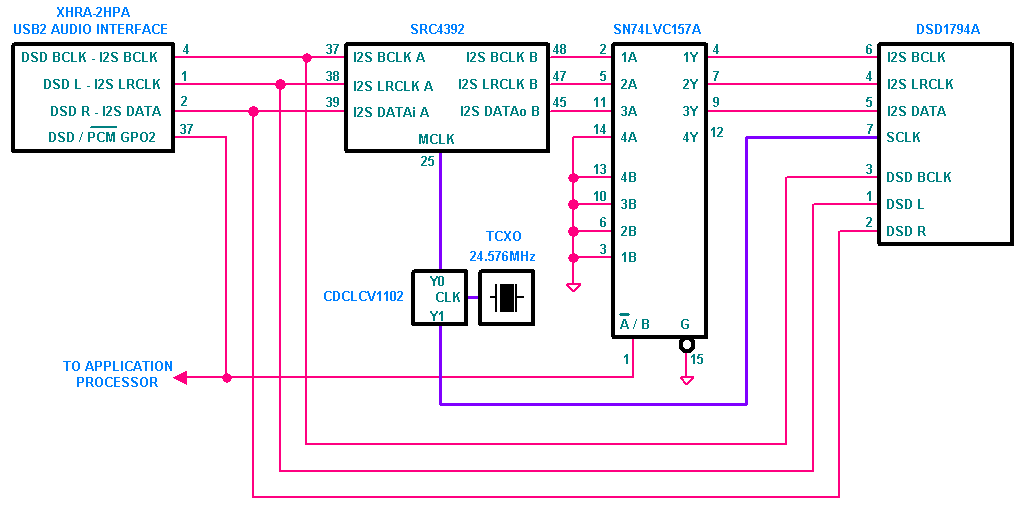

Another one question is that: It is worthy to i turn in SRC4392 instead DIX9211? I know a bit the benefits of async. sampling rate conversion. The only that bothers me is that, if we inject a DSD signal the SRC4392 will pass it to the SRC converter which is desirable only for PCM signals. Whilst DIX9211 does not includes a SRC converter and so is suitable to accept and route either PCM or DSD input signals at its I2S output. In the case of SRC4392 i think for DSD we have to use an external multiplexer before the DAC and i don't like it because i fear for jitter issues.

What do you think about that?

Thanks

Fotis