Hi,

I receive a question about the TLV320AIC3262 register settings from a customer. By a certain setting, TVL320AIC3262 does not output sound from HPR. I show an example of the failure of register setting.

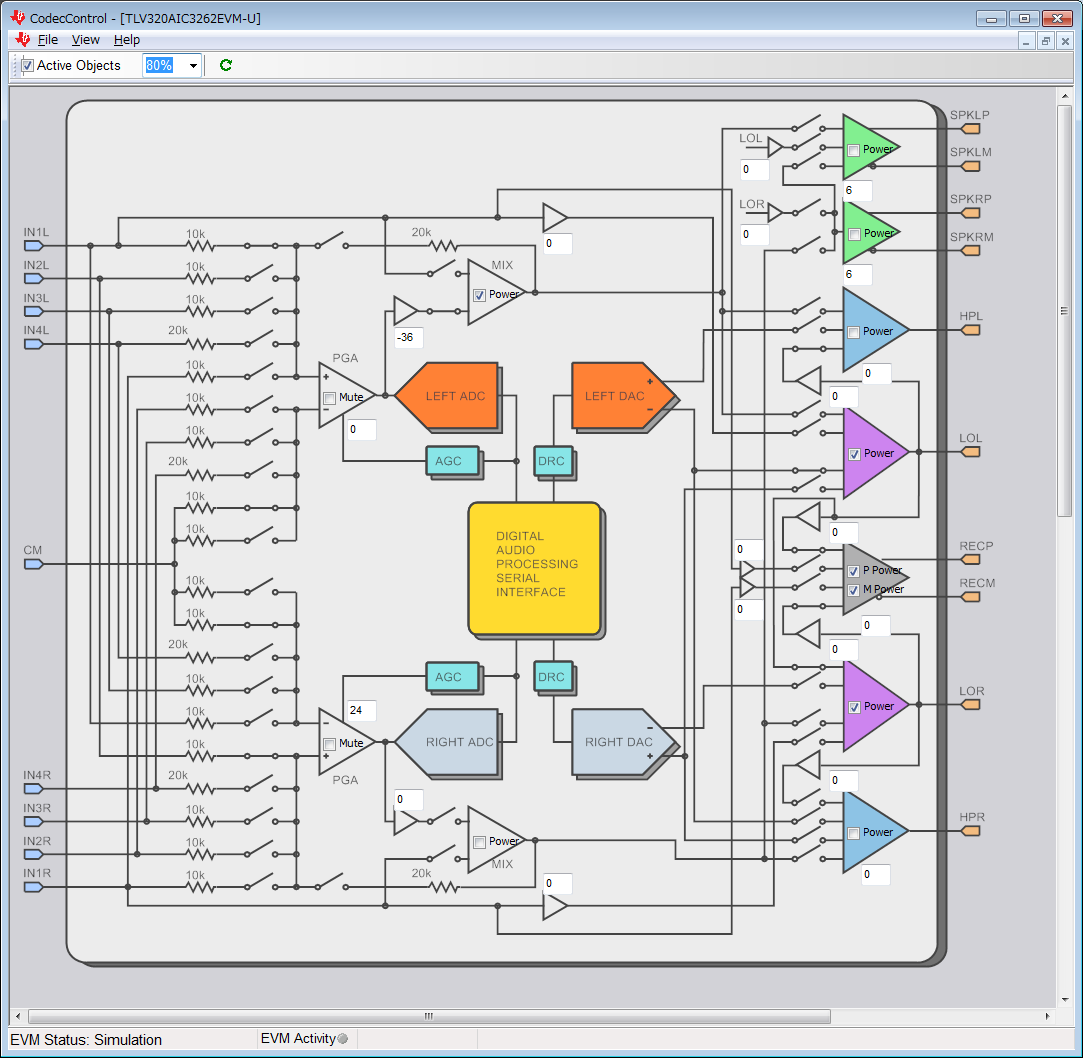

figure 1

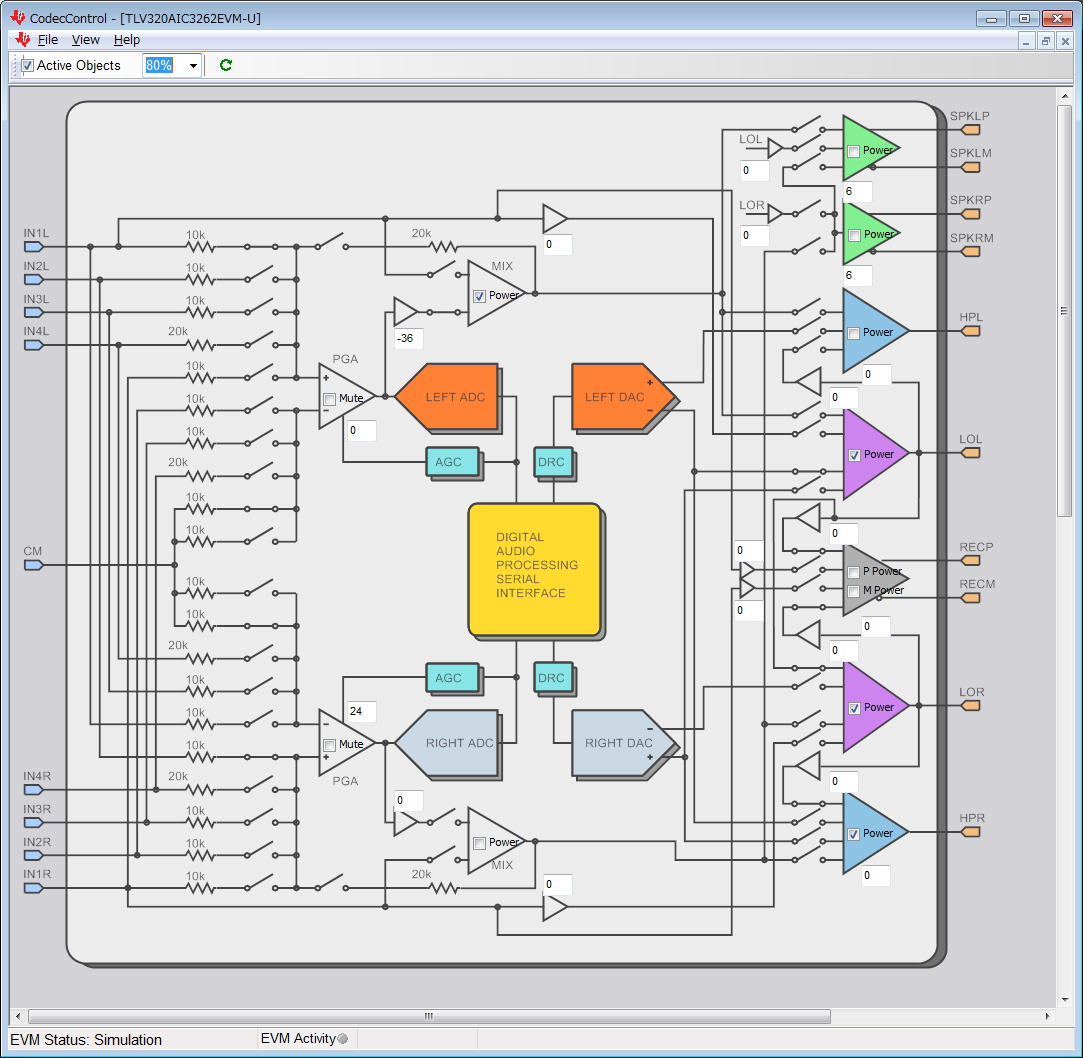

figure 2

Figure 1 is a setting the LEFT DAC signal outputs from RECP/M, and figure 2 is a setting the LEFT DAC signal outputs from HPR. Sometimes HPR does not output a sound when changing the path from figure 1 to figure 2. In this case, before the figure 2 setting, by addition to some register settings as shown below, HPR could output a sound.

B0_P0_R0 = 0x01

B0_P1_R27 = 0x03

B0_P1_R28 = 0x00

B0_P1_R31 = 0x80

However he can't insert these register settings because of software structure and lack of micro-controller resources. Is there any way of register settings to prevent the failure of HPR output? Up to now, HPL outputs a sound by similar setting. An example of setting is as follows.

B0_P0_R0 = 0x00

B0_P0_R127 = 0x00

B0_P0_R0 = 0x01

B0_P1_R55 = 0x00

B0_P1_R57 = 0x00

B0_P0_R0 = 0x00

B0_P0_R81 = 0x02

B0_P0_R82 = 0xc8

B0_P0_R0 = 0x04

B0_P4_R86 = 0x0c

B0_P0_R0 = 0x01

B0_P1_R52 = 0x00

B0_P1_R18 = 0x3f

B0_P1_R22 = 0x04

B0_P1_R36 = 0x38

B0_P1_R17 = 0x00

B0_P0_R0 = 0x00

B0_P0_R63 = 0x00

B0_P0_R0 = 0x01

B0_P1_R40 = 0x00

B0_P1_R40 = 0x39

B0_P0_R0 = 0x00

B0_P0_R64 = 0x0c

################ additional settings ################

*B0_P0_R0 = 0x01

*B0_P1_R27 = 0x03

*B0_P1_R28 = 0x00

*B0_P1_R31 = 0x80

#####################################################

B0_P0_R0 = 0x01

B0_P1_R59 = 0x80

B0_P1_R60 = 0xb0

B0_P1_R122 = 0x05

B0_P1_R51 = 0x3a

B0_P1_R58 = 0x00

B0_P0_R0 = 0x04

B0_P4_R10 = 0x01

B0_P0_R0 = 0x00

B0_P0_R19 = 0x30

B0_P0_R12 = 0x08

B0_P0_R11 = 0x02

B0_P0_R6 = 0x11

B0_P0_R6 = 0x91

B0_P0_R11 = 0x82

B0_P0_R19 = 0xb0

B0_P0_R12 = 0x88

B0_P0_R0 = 0x01

B0_P1_R51 = 0x7e

B0_P1_R58 = 0xff

B0_P0_R0 = 0x04

B0_P4_R10 = 0x00

B0_P0_R0 = 0x01

B0_P1_R122 = 0x01

B0_P1_R59 = 0x00

B0_P1_R60 = 0x30

B0_P0_R0 = 0x00

B0_P0_R81 = 0x42

B0_P0_R0 = 0x01

B0_P1_R55 = 0x01

B0_P1_R57 = 0x40

B0_P0_R0 = 0x00

B0_P0_R82 = 0xc0

B0_P0_R0 = 0x04

B0_P4_R87 = 0x0d

B0_P0_R0 = 0x01

B0_P1_R52 = 0xc0

B0_P1_R18 = 0x28

B0_P1_R22 = 0x87

B0_P1_R17 = 0x08

B0_P0_R0 = 0x00

B0_P0_R63 = 0x80

B0_P0_R0 = 0x01

B0_P1_R27 = 0x01

B0_P0_R0 = 0x00

B0_P0_R65 = 0x04

B0_P0_R0 = 0x01

B0_P1_R29 = 0x00

B0_P1_R32 = 0x00

B0_P0_R0 = 0x00

B0_P0_R64 = 0x04

B0_P0_R0 = 0x01

B0_P1_R28 = 0x7f

B0_P1_R31 = 0xb9

Best regards,

Akio Ito

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.