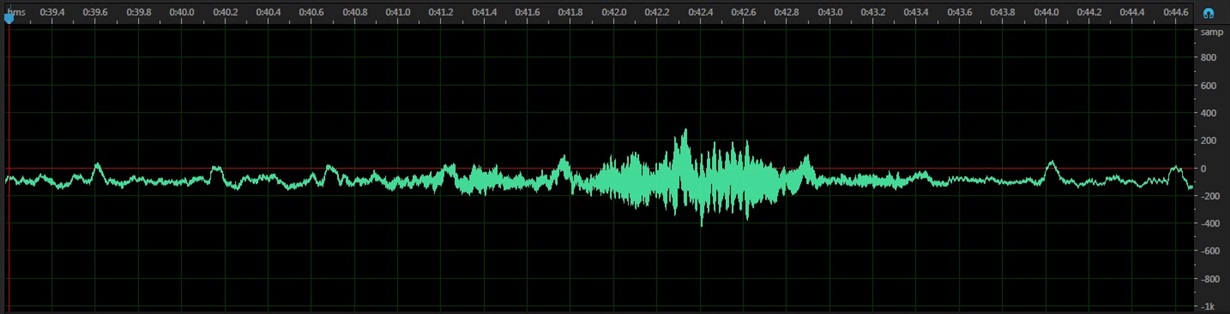

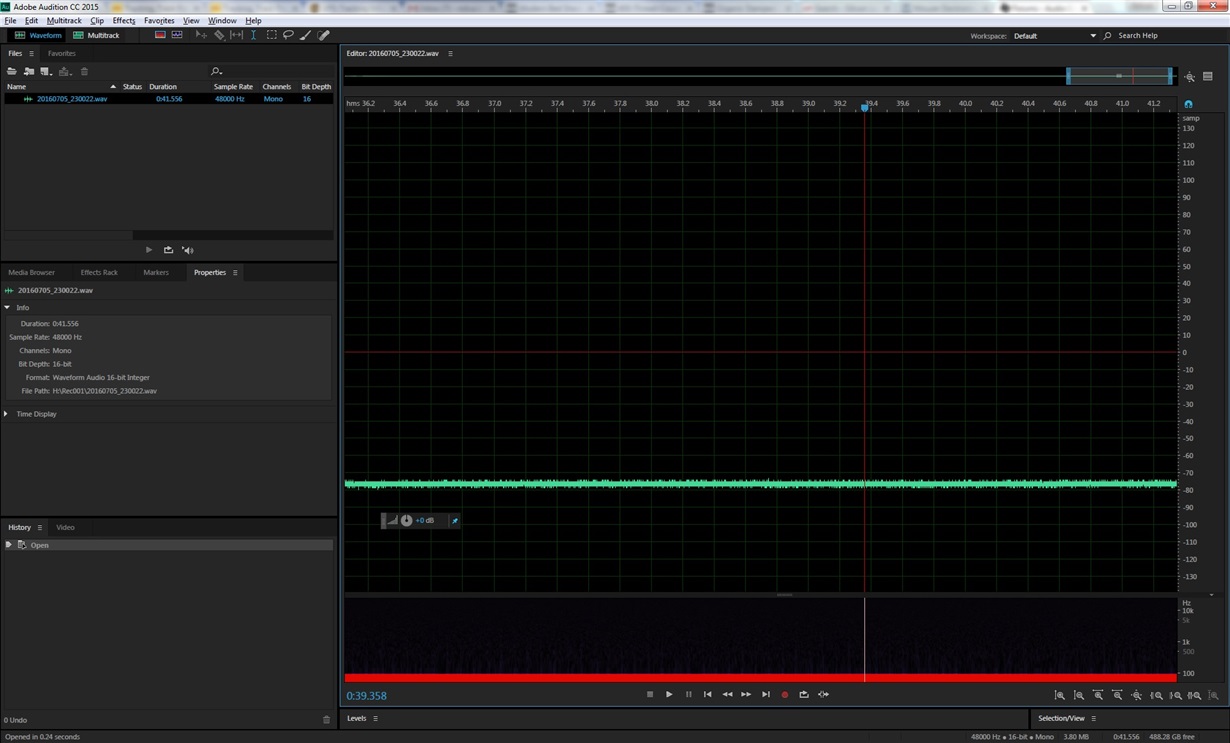

I'm working on a project using a TLV320AIC3204 CODEC and single ended microphone. The mic is a standard Electret type, and has a bias voltage applied by the MICBIAS output pin on the codec. The microphone signal passes through a 0.47uF coupling capacitor before entering the IN1_L pin on the the codec. The converted digital signal is read by a microcontroller and stored in a file. When I open the file in audio analysis software and "zoom in" on the graphically represented waveform, I see a small DC offset (i.e. the waveform is shifted above the zero line). I'd like to remove this offset, and I believe it's coming from the codecs common mode voltage.

I've set the common mode voltage to 0.9V to get the greatest dynamic range, and I notice the offset I'm seeing in the output is right at 0.9V

My first question: Is this expected behavior? And my second question: If this is expected behavior, is there a way to remove this offset in the output?

Thanks in advance for your help,

-Rob