Hello

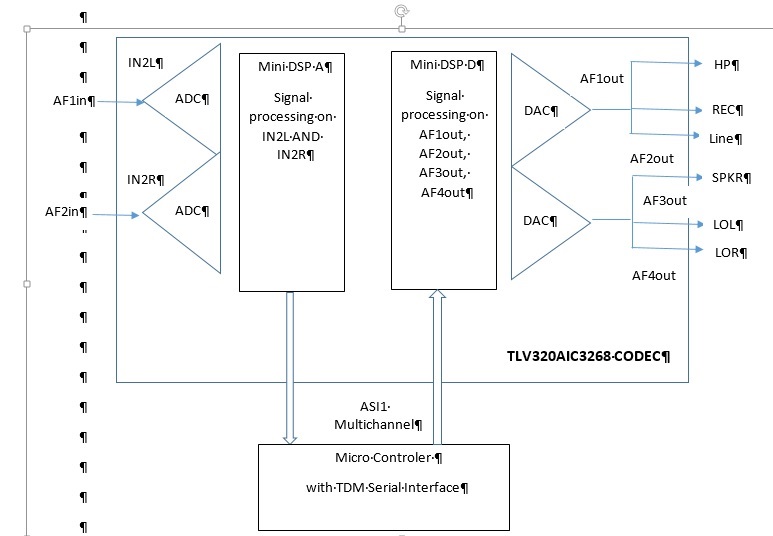

I Have to evaluate the TLV320AIC3268 CODEC.

I bougth the TLV320AIC3268EVM-U evaluation board, downloaded PPC2 and began testing with some scripts.

Now, I want to interface a MCU to the CODEC,to evaluate the ADC / DAC interface, this way:

- still using the PPC2 to configure the CODEC with the I2C port

- connect BCLK1, WCLK1, DIN1 and DOUT1 to the serial interface of the MCU in TDM or DSP format

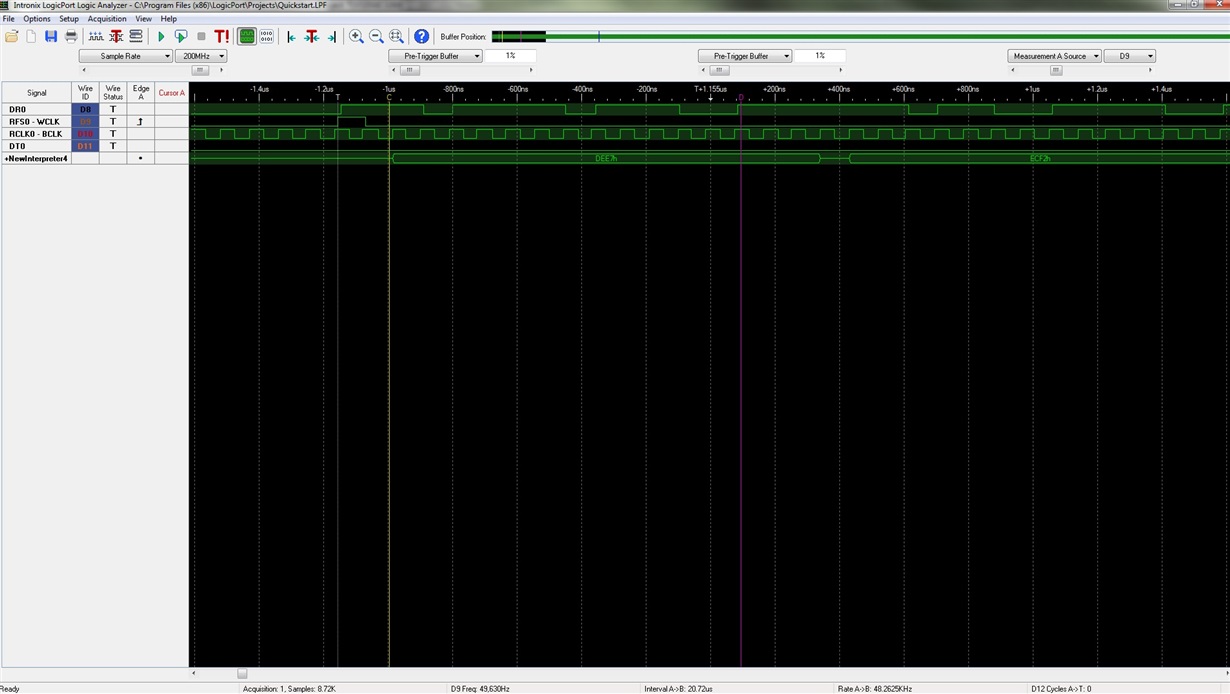

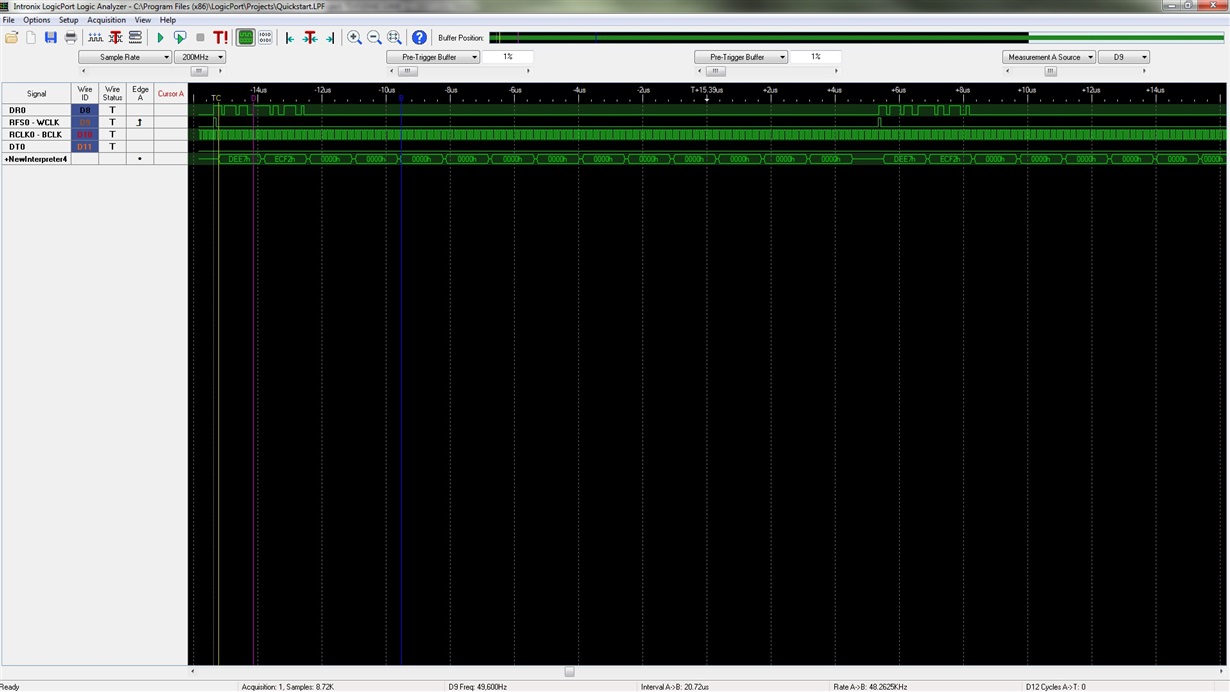

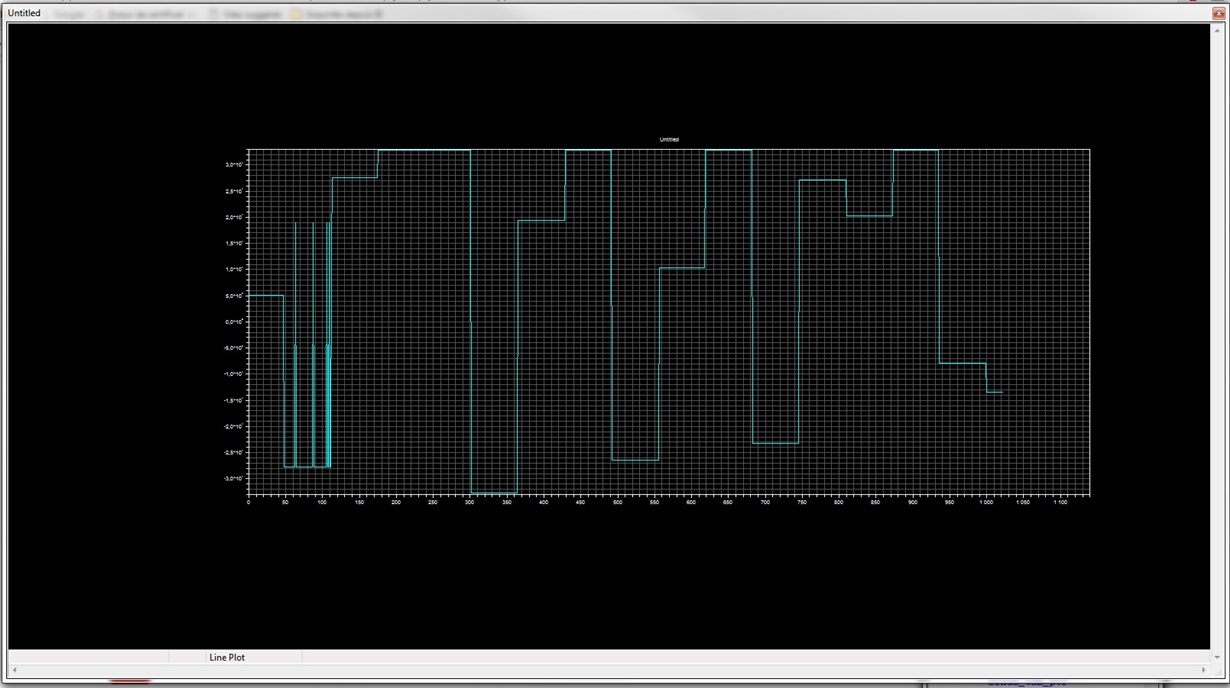

I tested different scripts, but I still have a 44.1 kHz clock on the WCLK1 output (on TP8) while using the script 6.2 (for instance) which should lead to: the following

Clock configuration

MCLK = 4.096 MHz, BCLK = 512 kHz, WCLK = 8 kHz (slave)

After what, every script I tested returns the same result (44.1kHz clock on WCLK1).

Could you please indicate me what is the issue? Is there any HW modification? jumper configuration? register configuration.. to do what I want

Many thanks.

Regards

Stéphane

I I j