Hi Team,

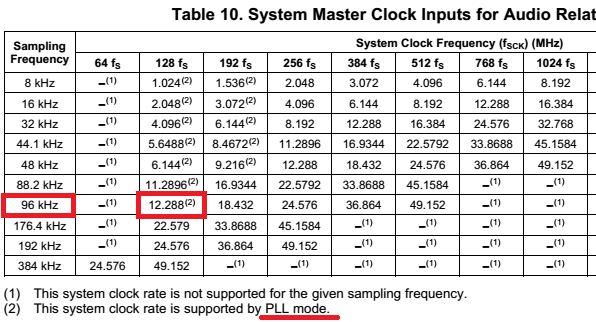

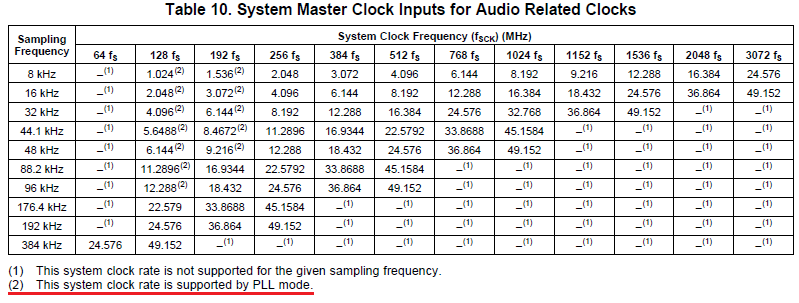

Table 10 shows "(2) This system clock rate is supported by PLL mode" as the following, however I couldn't catch what does it indicate.

Does it correlate somewhat with Table 11?

Best Regards,

Yaita / Japan disty

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.