Hi,

Our customer who is using TLV320AIC3107 designs a new model. He want to reuse the old design including power supply.

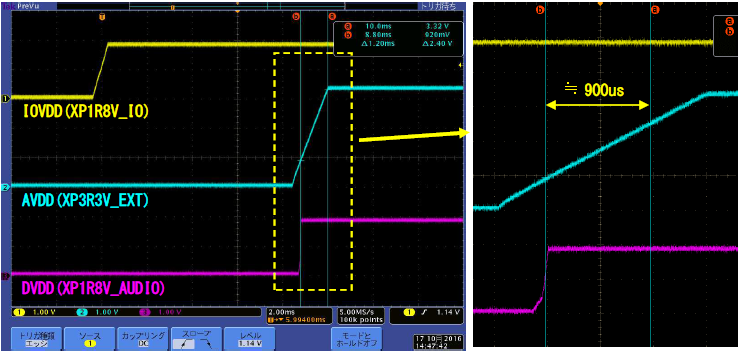

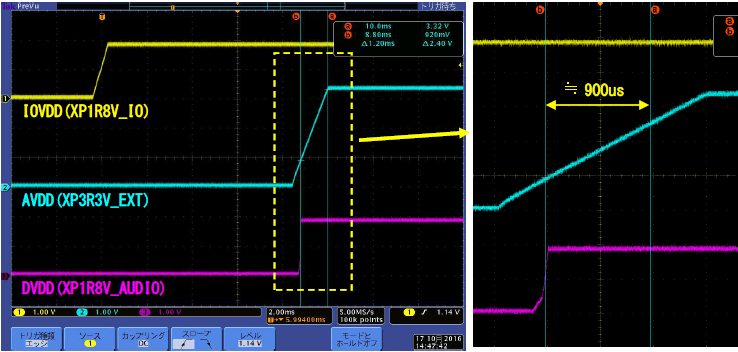

However, the design of old model can't follow the specification of power supply sequencing in spite of his circuit tuning.

I found that the specification of power supply sequencing had been added in revision D datasheet in December 2014.

e2e.ti.com/.../1319679

Q1. AVDD to DVDD maximum time of AIC3104 is 5 ms, but AIC3107 is 4 ms. Why are these different?

Q2. The datasheet before current revision did not have the specification of power supply sequencing for many years.

If he could not follow this specification, does his design have any problem?

Q3. If he could not follow this specification, are there any other conditions that he must obey at least?

Best regards,

Akio Ito