Hi

We have questions for FSOUT1 and FSOUT2 of DIR9001.

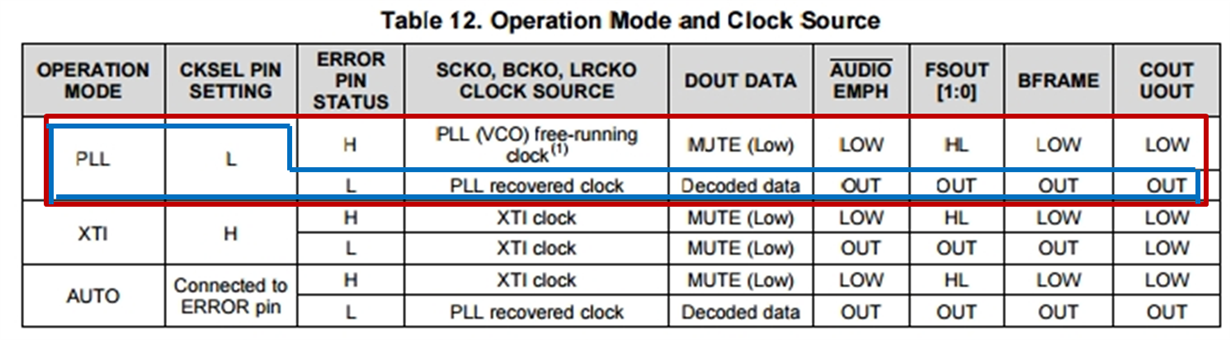

We are using DIR9001 without external crystal.

Sometimes, the state of FSOUT1=H, FSOUT0=0 is detected.

According to the datasheet, it indicates Out of range or PLL unlocked.

Questions:

1. What is the state inside the IC when the FSOUT outputs FSOUT1=H and FSOUT0=L?

2. What is the reason why the IC outputs FSOUT1=H and FSOUT0=L? Do you have any thoughts?

3. We want to clear the state of FSOUT1=H and FSOUT0=L. Could we clear this state by RST?

Or do you have any other recommended ways?

BestRegards