I'm interfacing with audio DAC TLV320DAC3120 with MSP430 controller and interface with Flash memory. I stored my audio tones in the flash memory .

I'm facing the issue at the time of playback the tone in the speaker. I am getting the noisy sound. But some time it’s playing the tone clearly. But coding remain same.

whether this issue is in hardware/ firmware side. Can you suggest me to solve this issue.

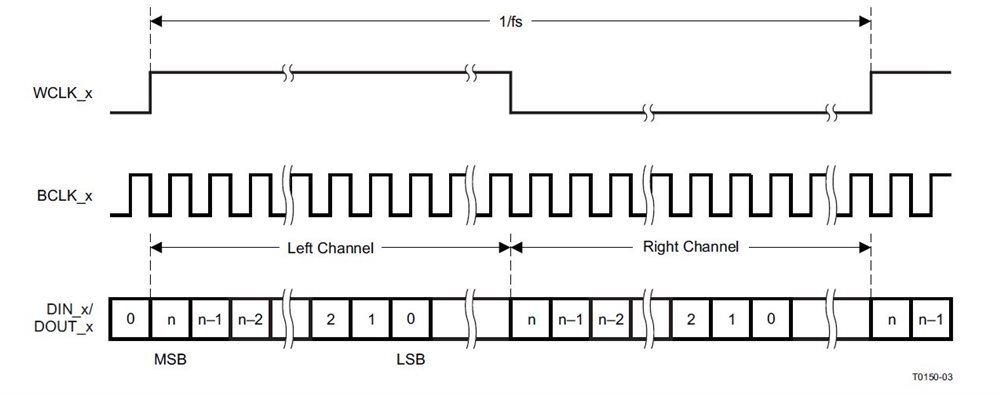

One more thing. BCLK signal is noisy in both the high and Low logic level.