Other Parts Discussed in Thread: AM3352

we are driving the codec via the McASP on an AM3352. we don't seem to have a problem communicating with the codec via I2C or the data lines

we are in DSP mode, 16 bit, 8KHz FS. codec is master for FS and WCLK. Input is a 24.576MHz oscillator. we are on a custom board, not an EVM

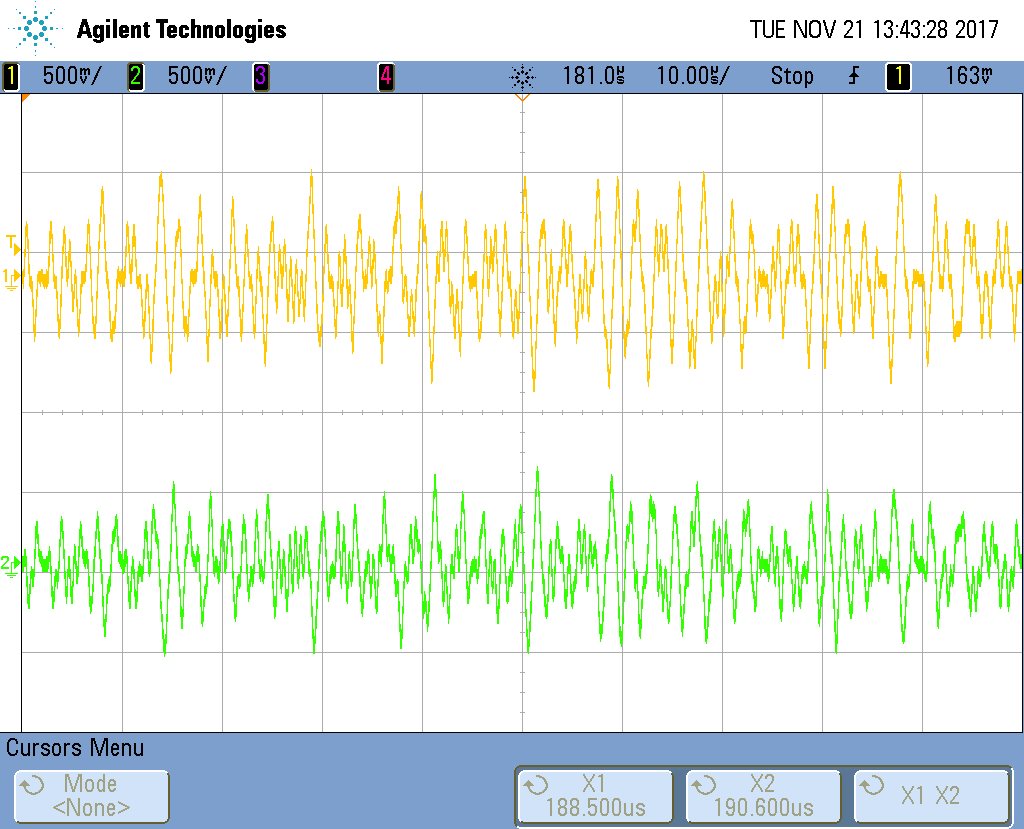

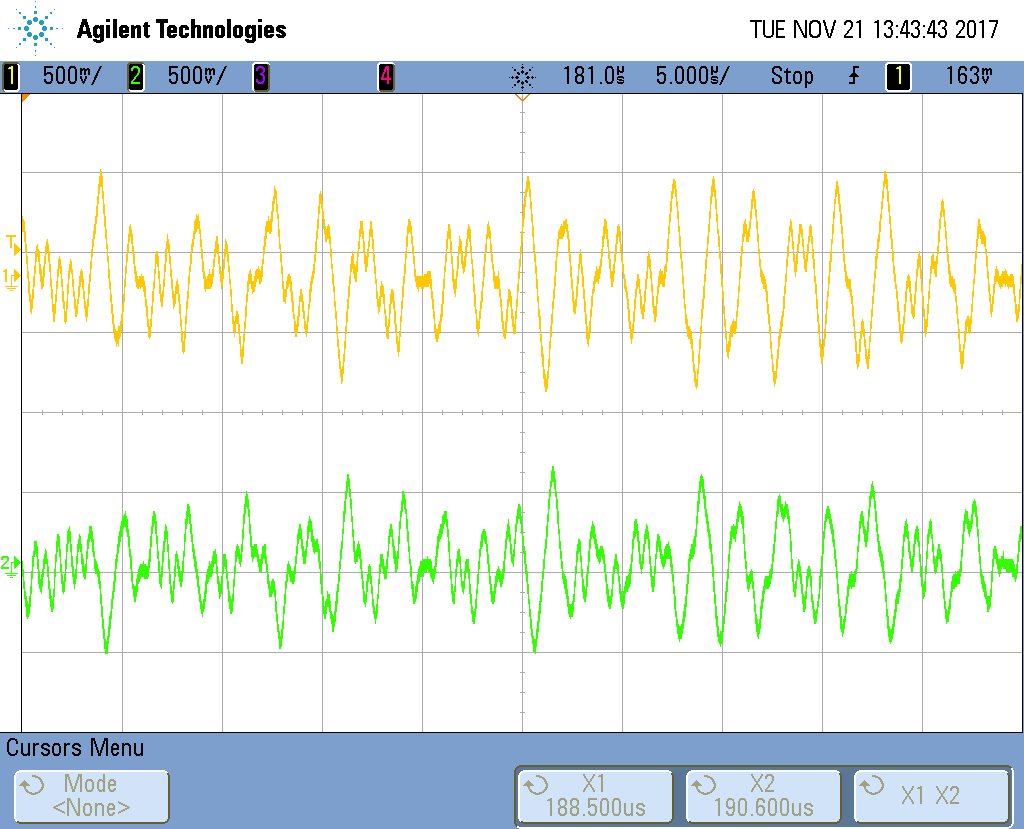

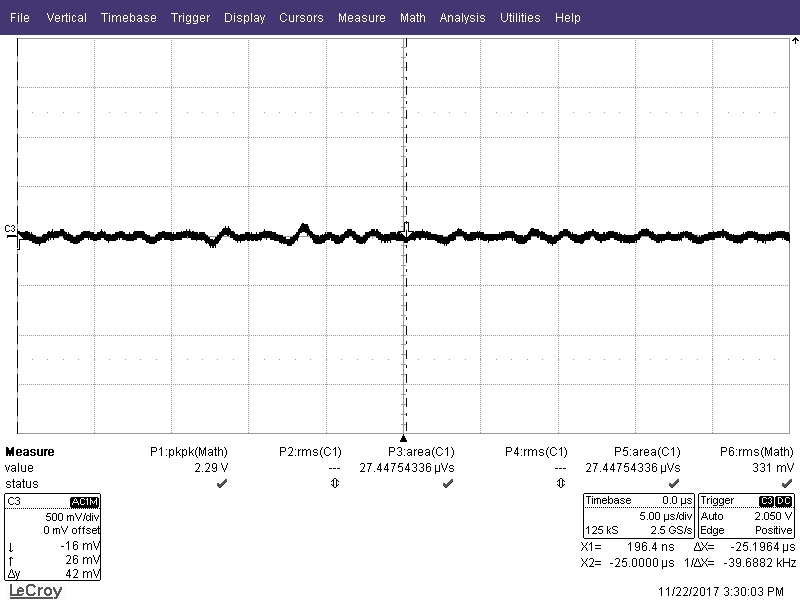

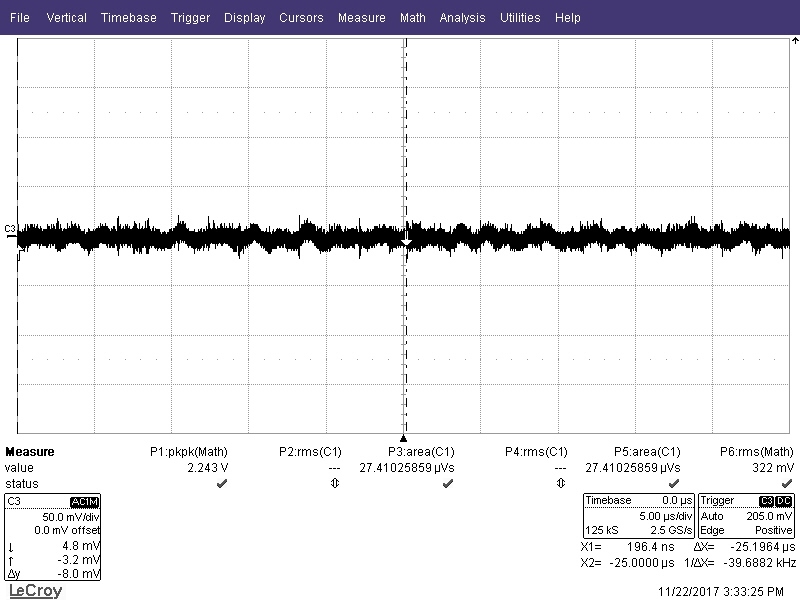

we have an issue with white noise on the DAC lines. it appears to be white noise. when audio is played out the DAC we can hear the audio but the white noise is always there. we are sending all 0x0000's to the codec for TX samples so it isn't the signal we are trying to play (it's hard to mess up 0's). if i mute the codec it goes away, if i apply gain to the DAC is appears. the amount of gain i apply to the DAC has no effect on the amplitude of the noise.

i should mention this is the first couple of days of using this codec so i am not an expert by any means.

we are using (for input) Line1L, Line1R, Line2R, Line2L and (for output) MONO_LO, HPROUT/COM, RIGHT_LO, LEFT_LO

here are the settings and the order in which we set them:

Reg 15 <- 0x80 (mute)

Reg 16 <- 0x80 (mute)

Reg 43 <- 0x80 (mute)

Reg 44 <- 0x80 (mute)

Reg 2 <- 0xAA (FS/6)

Reg 5 <- 0

Reg 6 <- 0 (D=0)

Reg 4 <- 0x10 (J=16)

Reg 11 <- 1 (R = 1)

Reg 3 <- 1 (P = 1)

Reg 25 <- 0x40 (2V micbias)

Reg 19 <- 0xFF (Line1L diff, Left ADC powered up, Left ADC no soft step, Line1L not connected Left ADC)

Reg 22 <- 0xFF (line1r diff, right adc powered up, right ADC no soft setp, Line1R not connected right ADC)

Reg 23 <- 0x80 (line2R differential)

Reg 78 <- 0x80 (DACR1 to MONO_LO)

Reg 89 <- 0x80 (DACL1 to RIGHT_LO)

Reg 61 <- 0x80 (DACL1 to HPROUT)

Reg 37 <- 0xC0 (right and left DAC powered up)

Reg 79 <- 0x09 (MONO_LO powered up, unmuted)

Reg 7 <- 0x0A (enable right and left data path)

Reg 9 <- 0x40 (DSP mode)

Reg 8 <- 0xD0 (BCLK and WCLK output, enable clocks to run)

one input is always on so that gets set

Reg 16 <- 0 (right ADC +0dB)

the system will then select a particular output when an action is done on the board:

we right set the gains for one input

Reg 16 <- 15 (right ADC +7.5dB)

then we set the gain for another set

Reg 43 <- 0x80 (mute left DAC)

Reg 20 <- 0xFC (unroute Line2L from left ADC, Line2L differential, Left ADC biased to common mode voltage - unroute for a CYA, is this needed?)

Reg 21 <- 0x78 (unroute Line1R off left ADC - unroute for a CYA, is this needed?)

Reg 41 <- 0x40 (Left DAC to Left Line Out DAC_L3)

Reg 19 <- 0x87 (Line1L differential, Left ADC powered up, Left ADC no soft step)

Reg 65 <- 0 (power down HPROUT)

Reg 93 <- 0 (power down RIGHTLO)

Reg 86 <- 0x09 (LEFT_LO unmute, powered up)

Reg 15 <- 0x0F (set ADC=7.5dB)

Reg 43 <- 60 (Left DAC attentuation -30dB)

and white noise. since i am so new to this codec i don't know if i am missing a setting. i didn't turn on any filtering or AGC, and i didn't see any settings after looking over all the registers that jump out at me for noise. i'm not asking you to fix my board if it is board noise, but if i am missing an important setting or setting up the codec wrong i would sure like to know. thanks.