Hi,

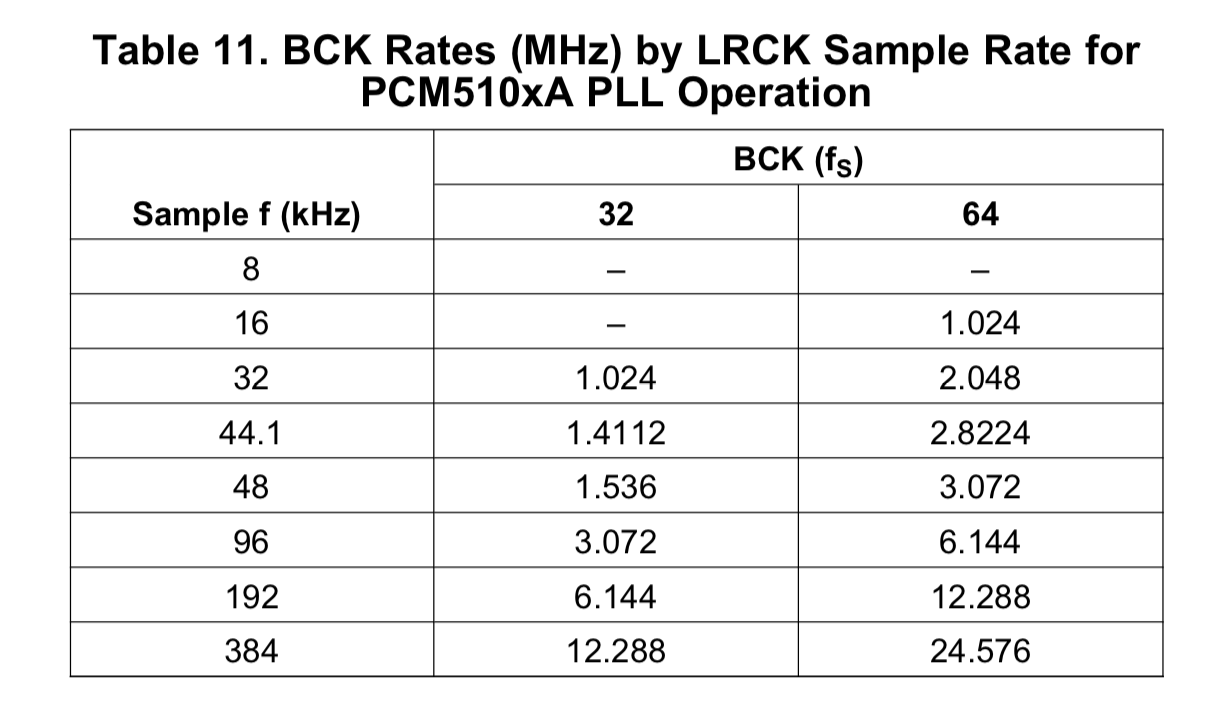

We would like to use the PCM5100A in a design, but we need the DAC to support 8 kHz sample rates with a simple 3-wire i2s interface (using the internal PLL to generate SCLK from BCLK). Our BCLK runs at 64*fs, but I am worried by Table 11 from the data sheet:

Is this saying there is no way use BCLK to generate SCLK in an 8 kHz application? If so, I'm wondering will it work but with decreased jitter performance, or will it just not work at all? If it's the former, we may evaluate if it's acceptable for our application.

Thanks in advance for any insight.

-Jay