Hello,

In our product AIC23 is connected to McASP port of DM642. The codec is configured as a slave device, using DSP mode. McASP is a master and generates LRCIN, LRCOUT, BCLK. McASP uses external clock, provided by pll1708. MCLK is 18.432MHz.

So far we used TDM mode with 32KHz frame sync, 3.072MHz BCLK, 16 bit word. This makes total 6 timeslots, from which 2 first carry left and right channels, four others are idle. Now we need to change the configuration to use BCLK 1024MHz, which makes 2 timeslots by 16 bits and no idle cycles.

The first question is whether this configuration (without idle bits) is valid?

The AIC23 datasheet shows some idle bits on all figures, describing digital interface, but doesn't say explicitly if they are required and how many.

I am posting this question, because with two timeslots we get unstable behaviour. After some startups all samples are duplicated. But if started well, it seems always works.

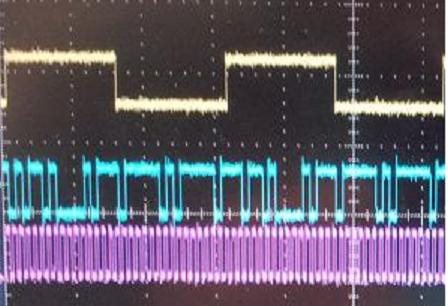

To illustrate the timings and the problem with duplicated samples I attached the image. The data starts on the second clock after rasing edge of frame sync.

If such configuration is valid, what could be other reasons for duplicated samples?

Thank you.

Best regards,

Dzmitry