Hello,

I'm serving as the packaging engineer for a company called ImagerLabs that has some great high-speed imager, low-noise imager chips which have been causing our customers to struggle with the off-the-shelf (14 bit, >40MSPS) multi-input ADCs as they try to design their cameras to fully exploit our imagers. The imager isn't the main noise source!

Any advice you could supply would be greatly appreciated, especially if a solution already exists.

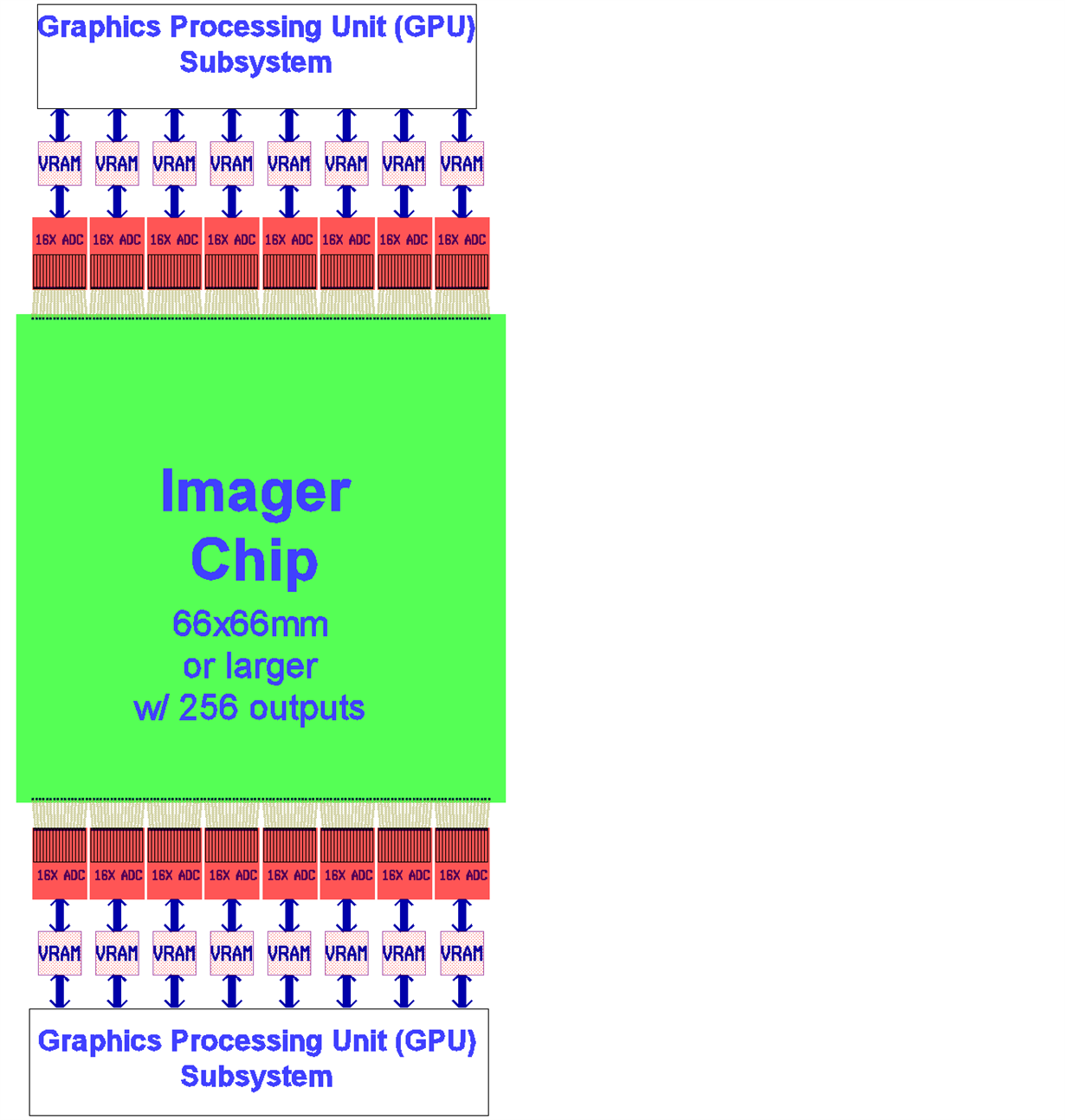

Some of the troubles stem from the electrical distances involved when trying to connect to packaged off-the-shelf ADCs so I'm very interested in a multi-ADC chip designed to be directly wirebonded die-to-die as described below and depicted in the image at the bottom (although I'm certainly open to any better architectures you could suggest). Note the sets of 16 "gold" wires shown between each 16 channel ADC chip shown in red and the big green imager chip. Exactly how the data is handled on the other side of the ADCs is wide open to suggestions.

Our imager chips usually have 2 opposite edges dominated with analog output pads, each needing an ADC. (We typically take advantage of gaps between these outputs by adding supplementary power supply pads, but these need not be of concern to the multi-ADC chip design.) We would take advantage of whatever ADC input pad density is available from a chip form suitable for direct die-to-die wirebonding where all the inputs are located along one edge. Currently, we have chips with 64 outputs on pitches of less than 0.5mm, and we could go much denser. Furthermore, our chips can be very large (we're already producing 61mm long runs of outputs; 2 runs per chip though not as dense as we'd like) so it would be quite advantageous if the opposite edge of each multi-ADC chip could host all the I/O needed for it to directly write to a dual ported memory so long rows of these ADC chips (and their companion memory chips) could be abutted into long strips along the edges of our imagers. I imagine the other port of each dual ported memory (e.g. Video RAM) to be connected to a mainstream graphics processor (GPU or DSP). Active cooling will be available since our imager chips benefit from that anyway.

At a minimum, 14 actual bits of resolution are needed at speeds of at least 40 MSPS, (preferably 2 to 4 times faster). The tighter the pitch, the better. Differential signals are also welcome. On-chip ADCs from CMOS foundries don't seem to be close to good enough, especially from process lines that make good imager chips. The ImagerLabs chips already on the market are demonstrating that high performance imaging is already significantly limited just by the available ADC architectures so we would like to tailor future designs to match next generation high-density, high-speed, high-SNR multi-ADC architectures. The image below depicts just one possible system layout.

This proposed architecture might be very useful to enough other scientific customers/applications that it may be quite possible to obtain government funding so I encourage you to think BIG.

For one nice example of why higher speed, higher dynamic range. lower noise imagers are still needed to understand our world, I invite you to view the episode of NOVA at:

www.pbs.org/.../edge-of-space.html

If you only have a few minutes, just skip to minute 31.

Thank you for your time,

Mike Fitzsimmons

ImagerLabs, Inc.