HI All ,

I Am working with ADS1018 and i having some issue , below is my configuration settings

ADS1018 VDD = 4.096V (Reference Voltage)

Analog Input #0 =3.5V (Constant Voltage)

Analog Input #2-#4 =0V

Configuration = 0x426b

------------------------------

Single ended mode

Continuous conversion

PGA=1

DOUT/DRDY pull up Enabled

NOP=Valid data, update the Config register

MUX[2:0]= AINP is AIN0 and AINN is GND

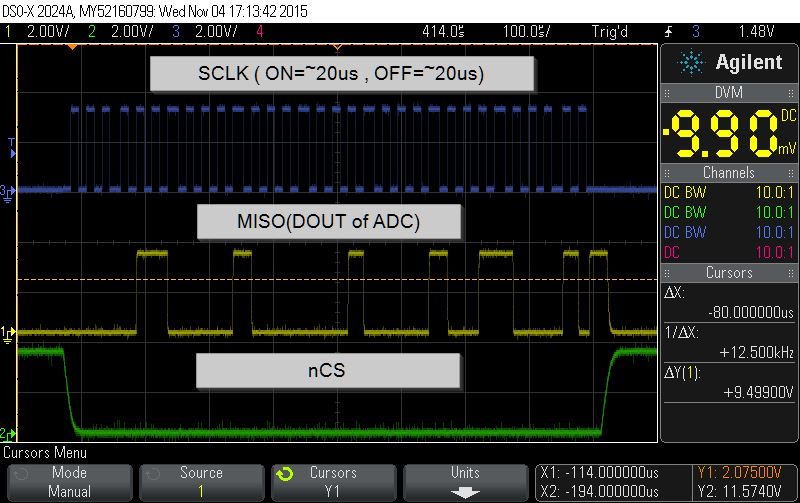

my transmission cycle is based on (32bit Data), during this cycle i am sending my configuration twice.

I have manged to read correctly reading (with the configuration read back as expected) , when i start transmission cycle i am lowering

my nCS to '0' , and check DOUT/DRDY if '0' meaning new reading is available and continue with transmission cycle,

else ( '1') new Reading is not available , in this case i don't continue with the transmission cycle and return nCS to '1' .

my problem is that sometimes the ADS1018 is 'Stuck' (DOUT/DRDY is '1' when i am lowering nCS to '0') no matter how much time i am waiting between

each iteration (each time is ~100ms) , can anyone please advise ?